Using PTH12050W with Vin = 12V, Vout set for 5V or 3.3V. Track pin is tied to VIN and Inhibit pin is unconnected.

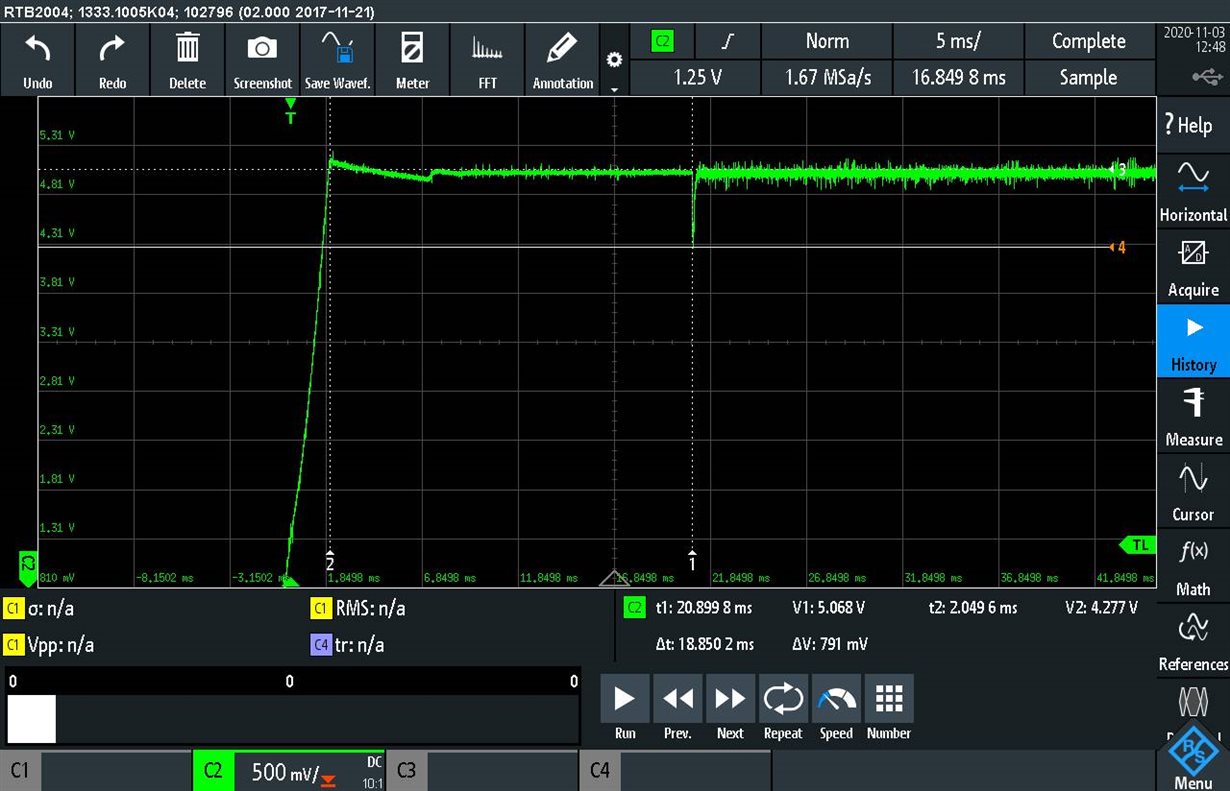

When the module is powered up with zero load or near zero load, a glitch in the output is seen after about 18 ms, and switching noise becomes more pronounced.

See plot below for 5V output module.

What is the cause of the glitch?

I suspect this has something to do with the module completing its soft-start initialization and then wanting to follow the Track input.