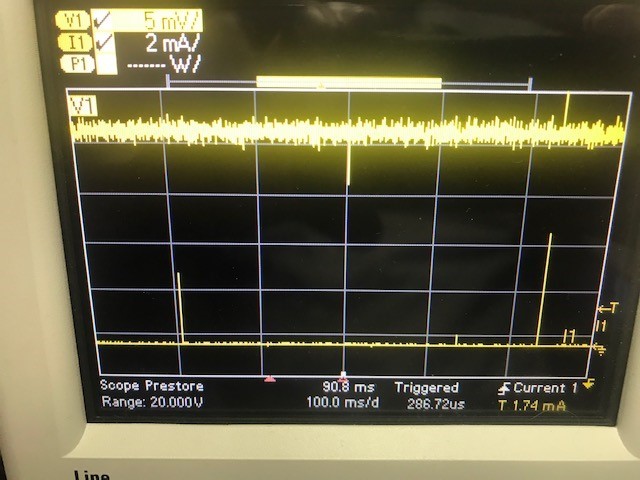

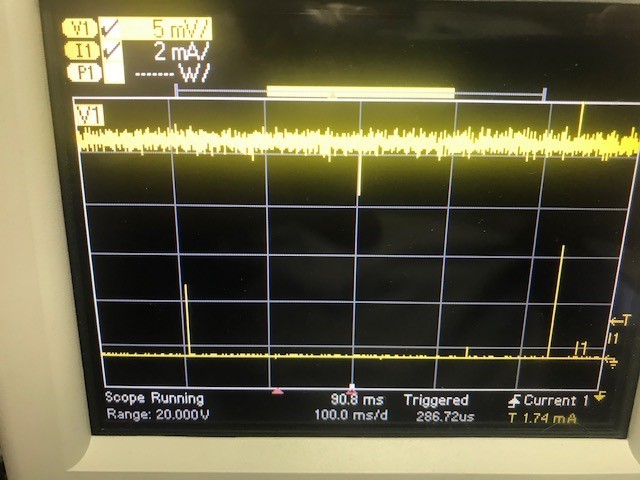

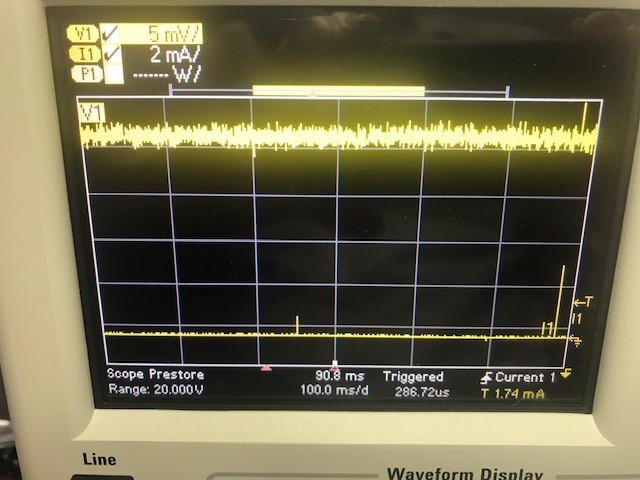

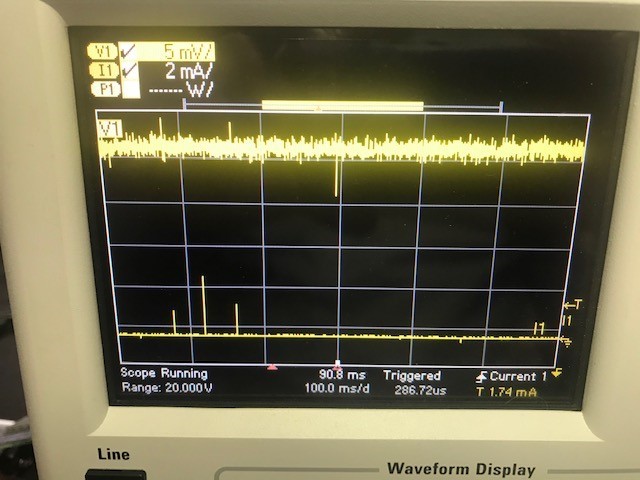

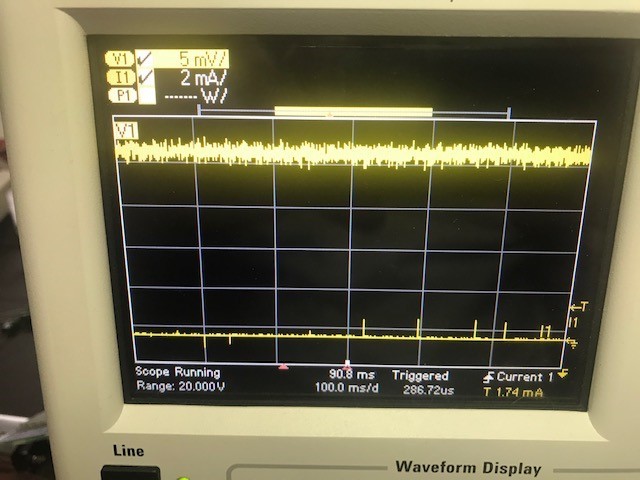

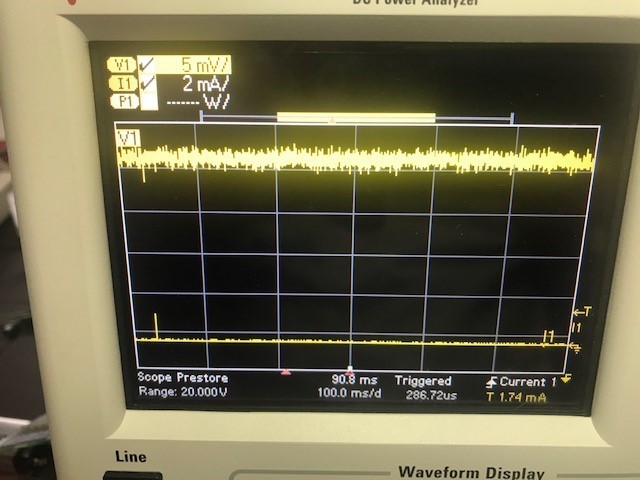

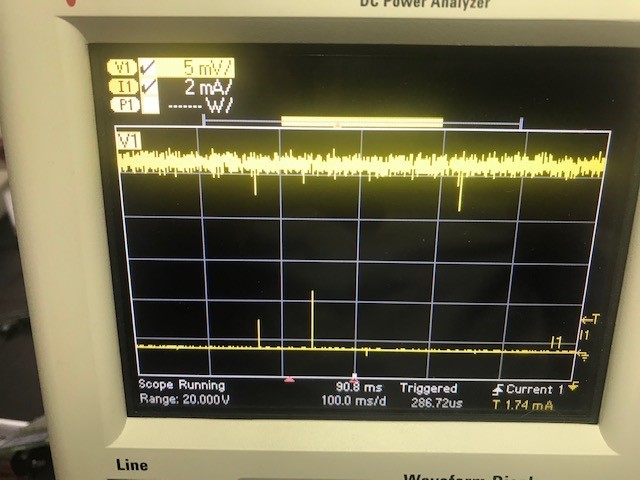

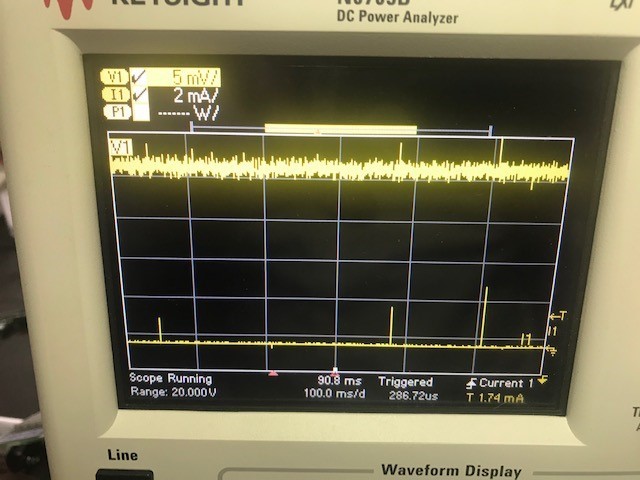

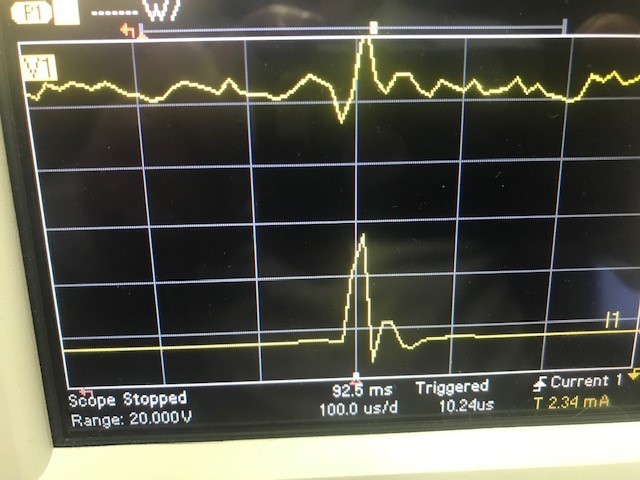

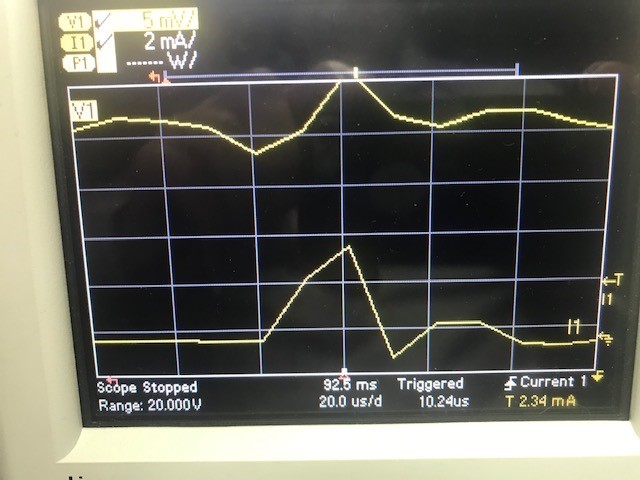

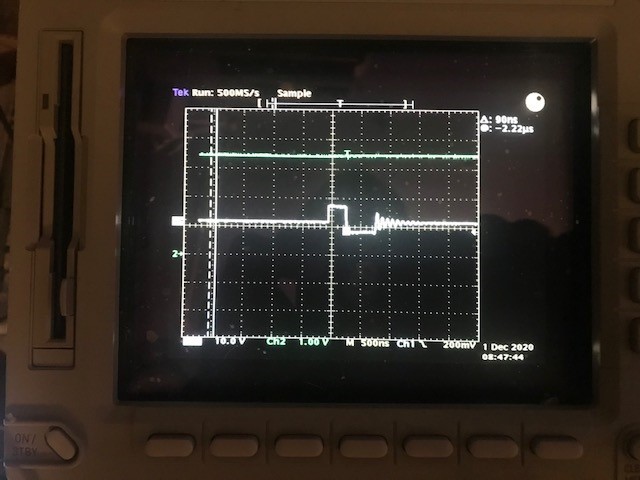

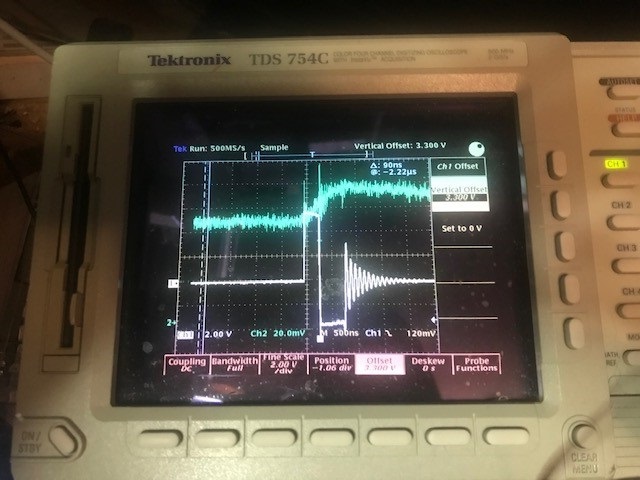

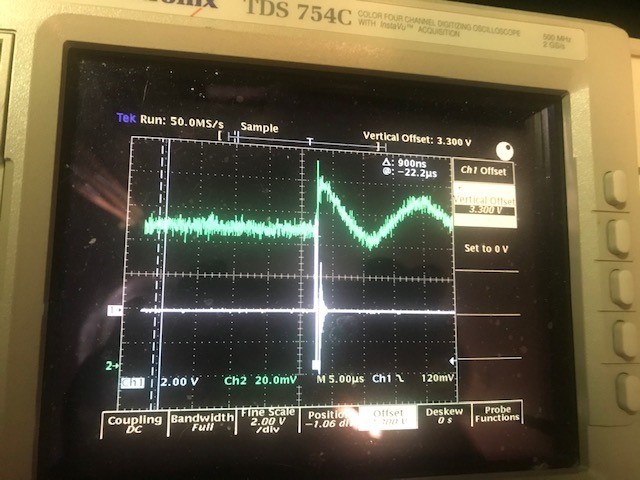

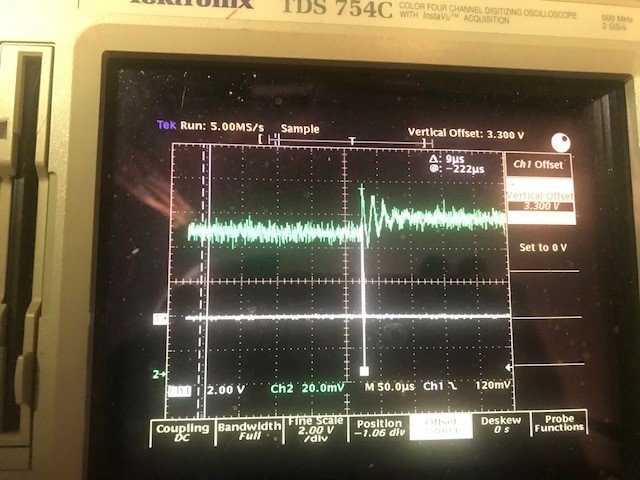

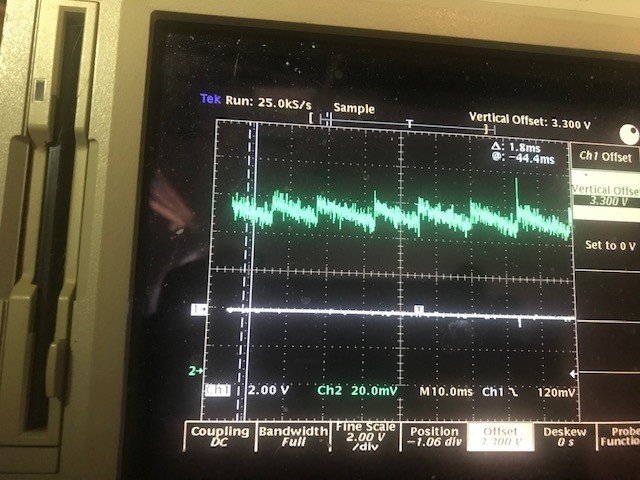

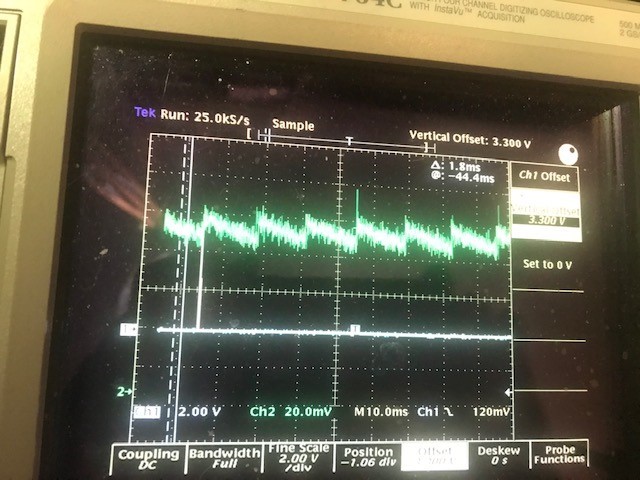

I am using the TPS62745 in a low current design, and every so often, I get a large (> 5mA) current spike. The period of the spike seems to shorten as load increases. Also, over multiple units, the period varies. I suspect the TPS62745 because the circuit is broken before any of the down line circuits (only the power subsystem) and I can still observe these spikes.

Anyone have ideas of what is possibly occurring ??

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.