Other Parts Discussed in Thread: BQ78350-R1, , TIDA-00449

Hello.

We are trying to build a BMS using the BQ76930 AFE and the BQ78350-R1 Fuel Gauge. Design based on EVM. Generally, it works fine, but we not sure if short circuit protection works properly. We are using 10S4P battery configuration. We tested with 5 and 10 mOhm shunt resistors, also we tested with different SCD delay 70-100uS, as a result, all times CHG and DSG FETs and shunt resistor were damaged. After we busted few FETs, we had added bulb as load and continue testing. A bulb has huge power consumption at the start, more than 50 Amps it helps emulate SC in "safe " mode, we recognised that SCD delay had been working not properly.

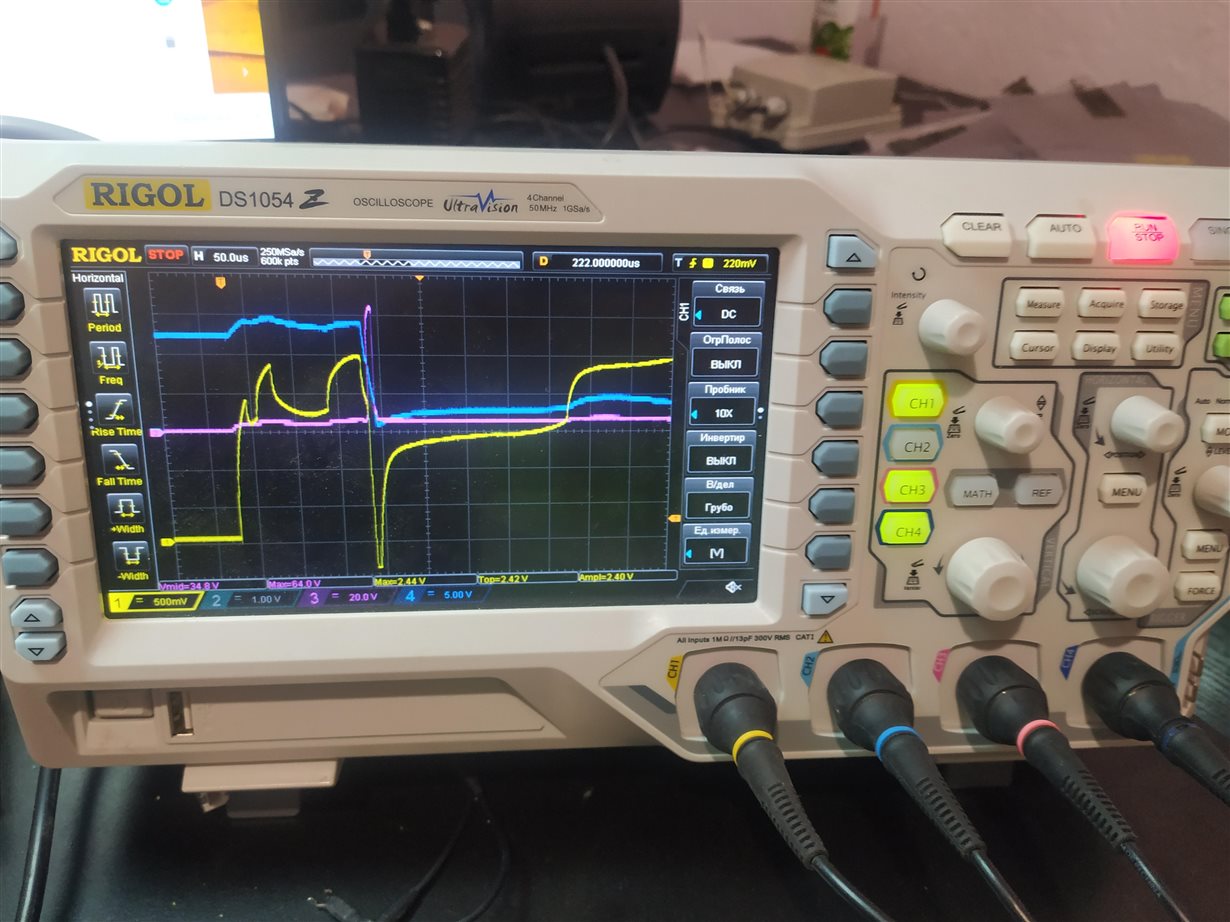

Figure 2.Test with bulb. (Yellow is the voltage across the sense resistors, Rsens -10mOhm)

As you see it's wasted around 6+mS for disable FETs.

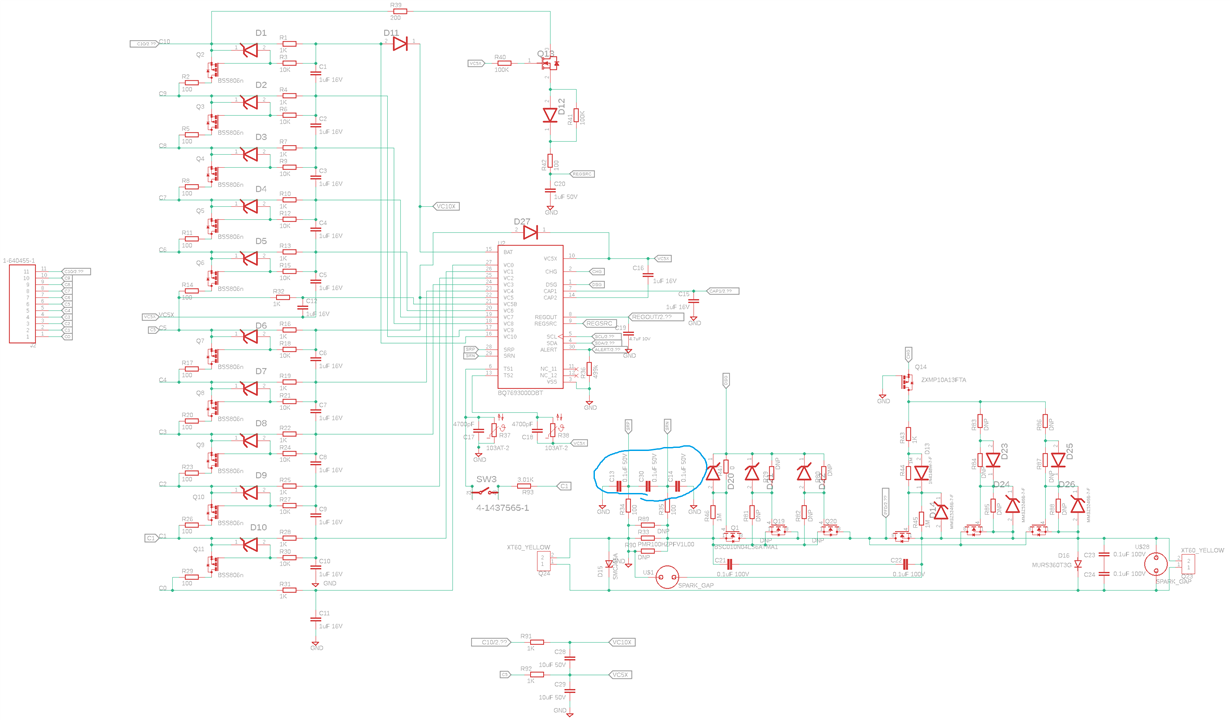

Figure 2.BQ76930 schematic (Was used 1 CHG FET and 1 DSG FET and 1 shunt )

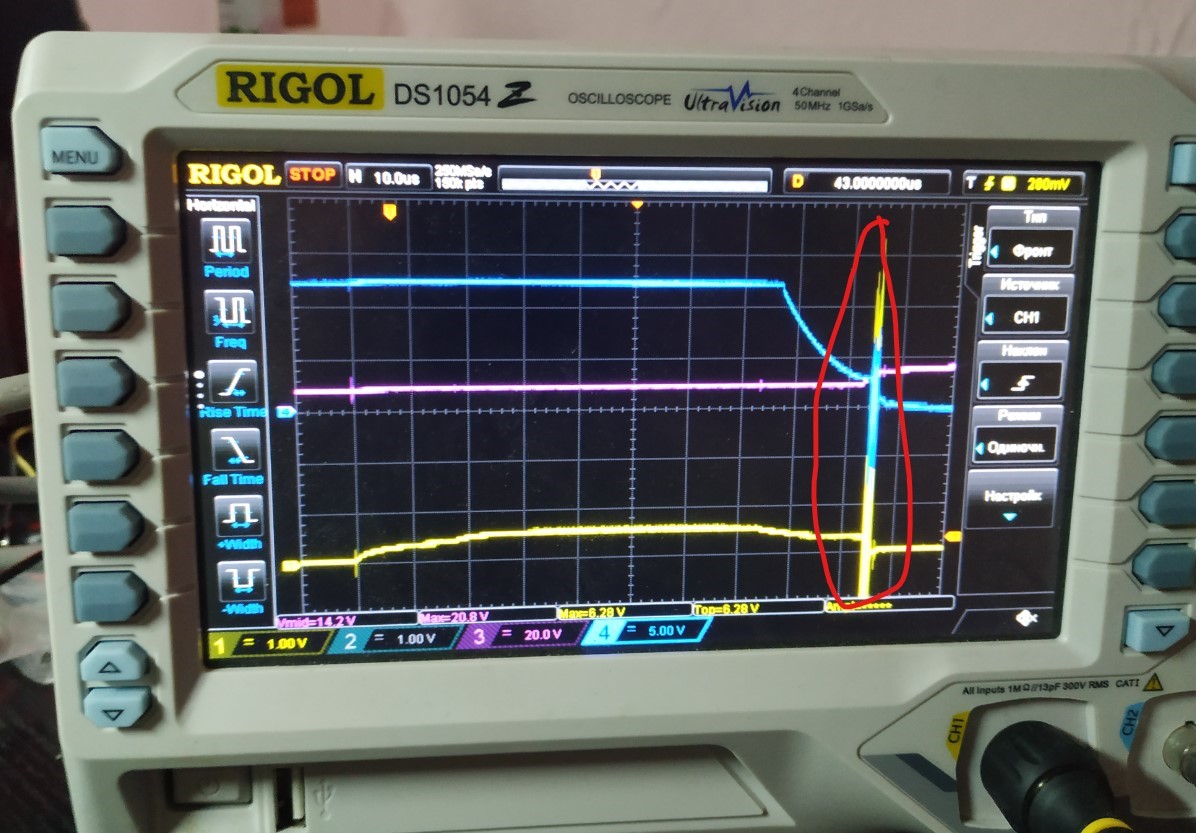

After a few experiments, we have changed C13, C14 and C30 capacitors to 1nF and got not bad result like 150uS when short circuit discharge delay is 100us. But when we had removed the bulb and had made SC test CHG and DSG FETs and shunt resistor were damaged.

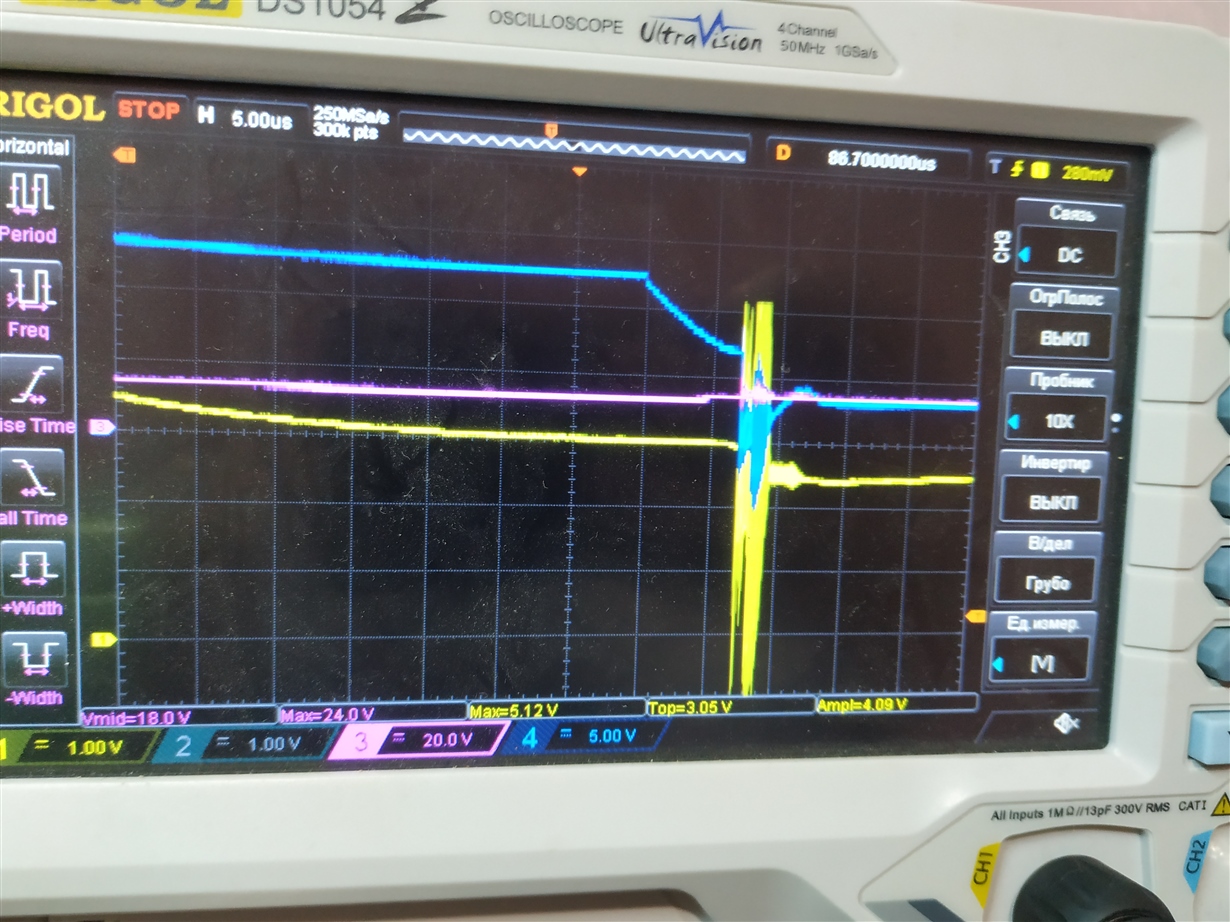

Figure 3.Short-Circuit Test(Chanel1 is the voltage across the sense resistors, Chanel 3 is the CHG FET gate voltage, Chanel4 is the DSG FET gate voltage, Rsens -10mOhm. Components were damaged).

What minimal SC delay? 70uS?

Strange situation with CHG FET gate, could you confirm is it ok?

Do you have some recommendation to solve it an issue?