Other Parts Discussed in Thread: TPS546B24A

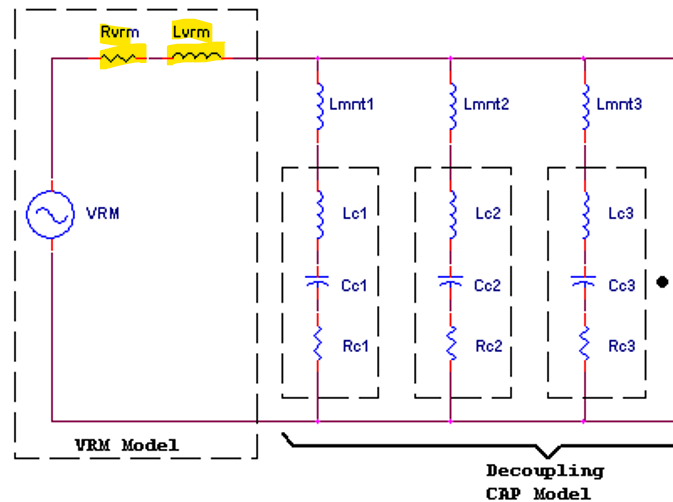

I am trying to model a power distribution network, and would like to extract the output impedance of our design with TPS546D24A. It is also called the VRM model, as here.

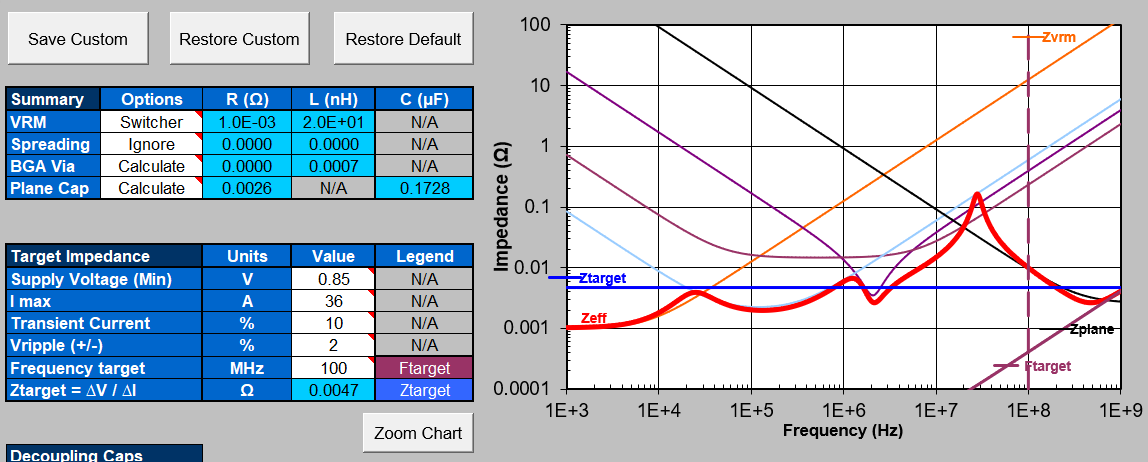

I would like to use it in an Altera PDN modeler, imaged below. The impedance is mainly determined by the control loop parameters.

How can I calculate the closed loop output impedance with the data TI offers me in the DS?

Thank you,

MA

The model:

Sample impedance graph without MLCC caps: The orange line is the modeled VRM impedance,