According to the TI white paper Optimizing GaN performance with an integrated driver

I have some question I would like to ask

1.) The yellow line, what is the resistor, is the GS resistor?, what is the L-R-C tank look like can someone give me a figure?

2.) in this paper, the simulation figure is using TINA-TI? or what? I want to learn this part. Does the TI provide the simulation file?

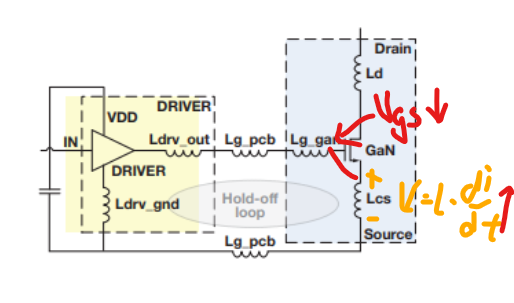

3.) In this figure, (a)(b) are have LcS common source inductance, I still don't understand what LcS affect our drive circuit