I am dealing with some ringing on the SW node of my TPS61165. See the oscilloscope shots below:

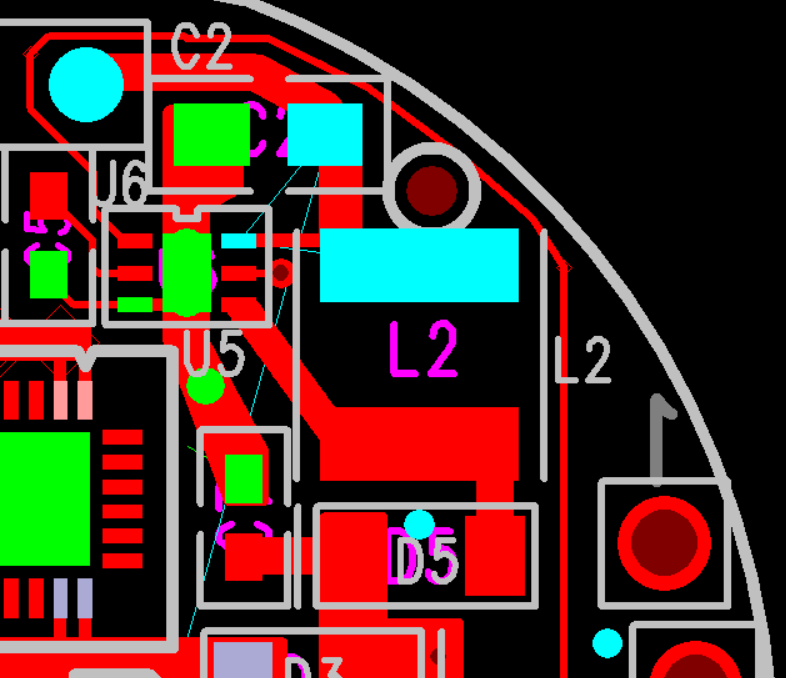

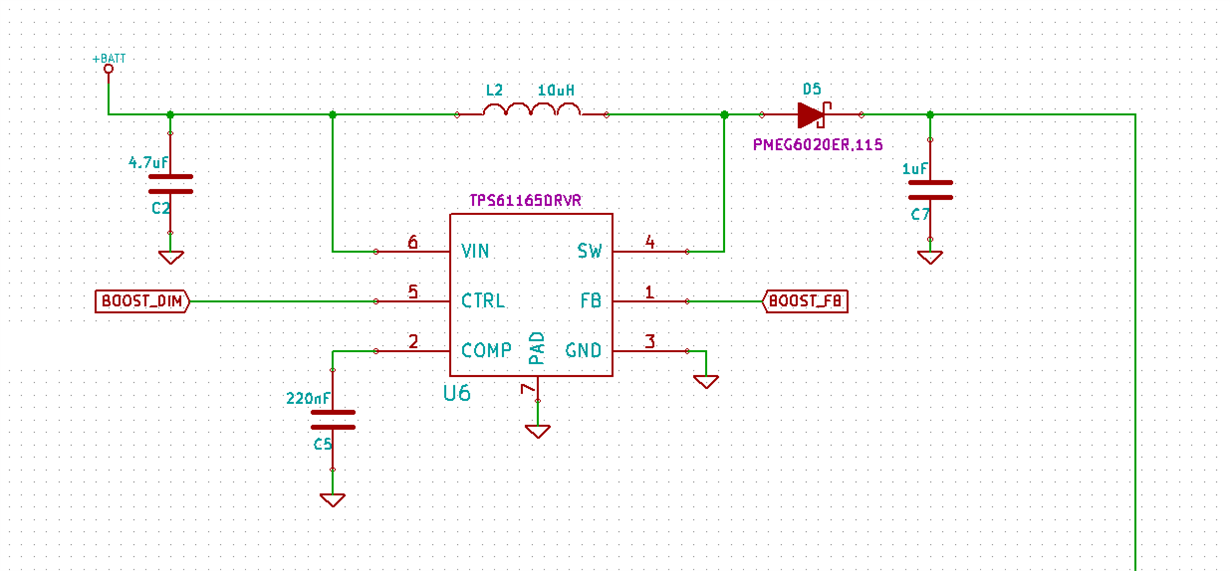

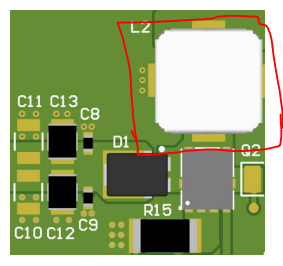

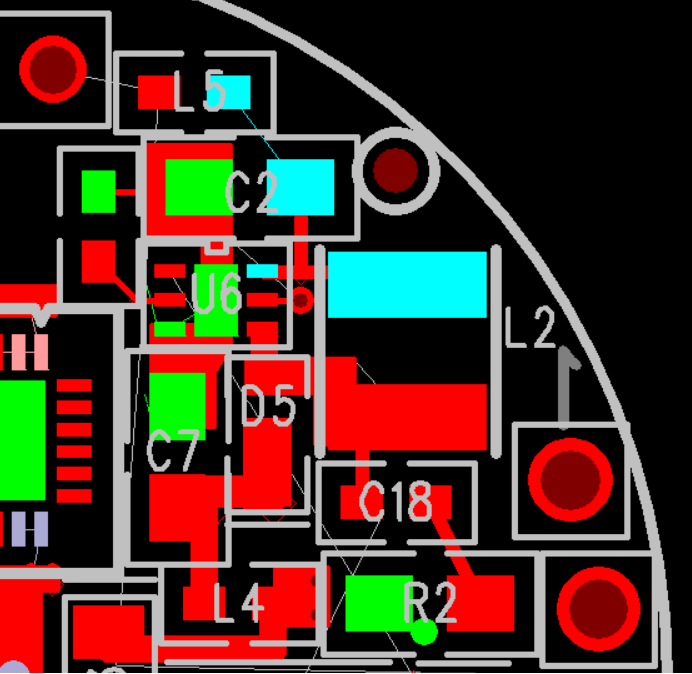

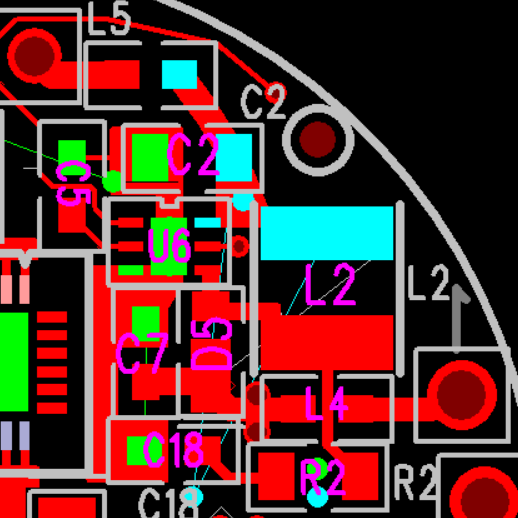

My layout is, I think, pretty good. But please let me know if anything looks off about it:

There are two vias to ground under the thermal pad. It is a 4-layer PCB with a solid ground plane on layer 2.

Are there any solutions that you can recommend that are specific to this device? Or can you point me towards a general-purpose solution for this sort of ringing?