Other Parts Discussed in Thread: , TPS548A29, TPS22810, TPS25982, TPS24751, TPS546D24A

Hi,

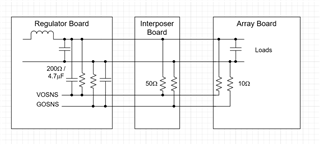

I am designing a regulator board that will convert 12V to 1.8V with 35A max current and thinking about using TPS546C23 as one of the regulators. While going through the IC and EVM datasheets I was not clear about the following things:

1) In the SOA curves given in the datasheet in Figures 20-22, what does "Natural Convection" mean? Is that the same as "no fan and no heatsink" used? I plan to go 2V max Vout and fsw = 500KHz with this regulator. If my max Ta = 50C, what is the max current that this regulator can support without affecting part reliability and overheating? I do not plan to use a fan or a heatsink and would not like the TJ to exceed 125C.

2) In "TPS546C23EVM1-746" user's guide, the Vout ripple shown in Fig 9 and Fig 10 for 0A and 35A load current doesn't change at all. Why is that? I always thought that ripple is a function of load current.

I will post more questions next week. Can you please answer the above in the meanwhile?

Thanks,

Noman