Hi,

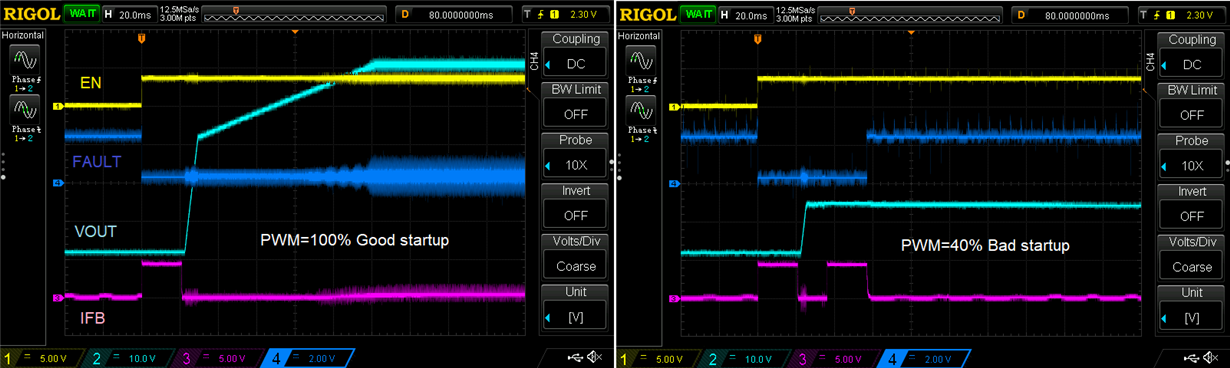

We are having a strange issue whereby the IC does not start-up unless the PWM input signal is higher than around 50% cycle. It seems that the DC-DC converter fails to start if the PWM pulses are too short. We can see the output voltage rising (GDRV starts switching) but then it stops shortly after that.

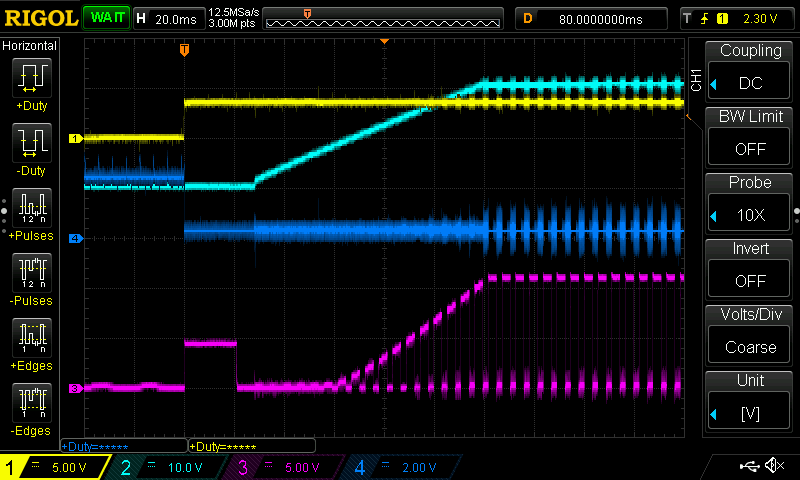

Our work around is to increase the PWM duty-cycle (= longer high pulses/same frequency) at first start shortly after setting EN pin high and for a duration of 20ms or so before falling back to a lower PWM duty cycle.

Once switching happily we can actually lower the PWM duty cycle down to approx. 0.5% (minimum we can achieve with our controller) with no problem. We use clean 0V to 3.3V signals for EN and PWM and a fixed PWM frequency of 200Hz.

Does the converter need a high PWM duty cycle to start-up properly (during the soft-start period maybe)? Also is there a recommended time to wait between enabling EN and the start of PWM dimming?

Thanks