Hello,

This is probably not an issue with the actual UCC21750 driver, but likely something to do with the gate drive loop - I wanted to see if anyone on here has experience with paralleling SiC power modules and the gate drive implications therein.

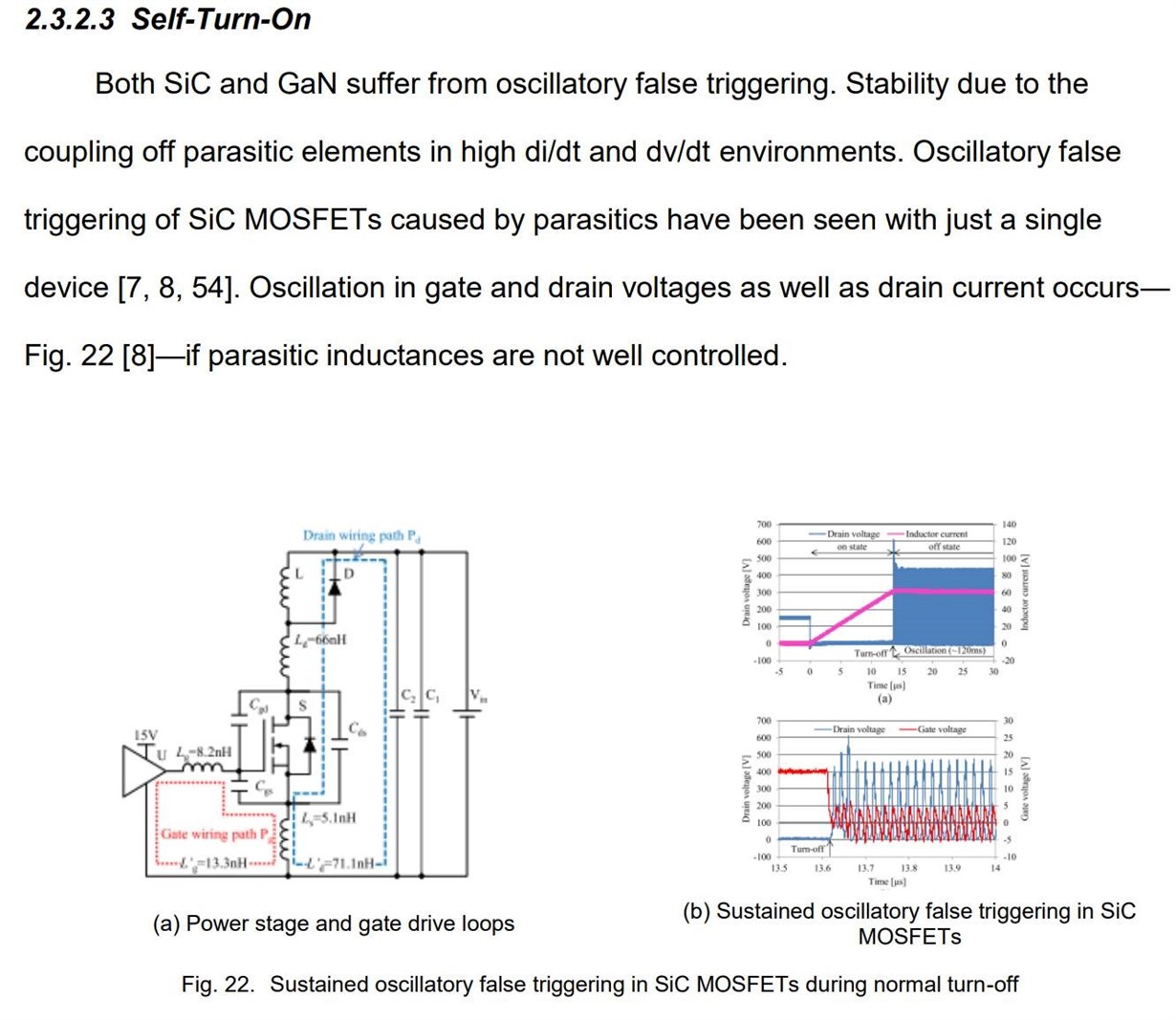

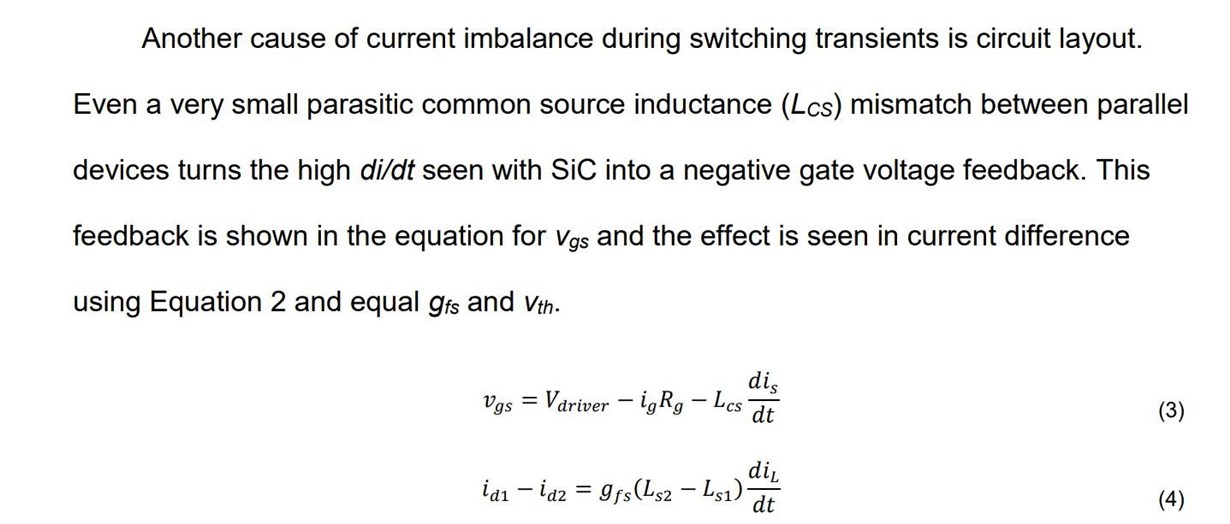

We are designing a 3-phase power converter that needs to switch an 880V DC bus at 470Apk, and to do this we have decided to parallel two cas325m12hm2 modules and drive them with a BJT buffer stage off of the UCC21750 gate drive output. To initially prove out our design we have made a single channel gate drive board which we are running simple double pulse tests with, and are experiencing some oscillatory behavior at something like 16 and 33MHz on the gate-source and the drain-source waveforms.

The BJT for the current buffer we are using here is the QS5Y1 due to its quick turn-on

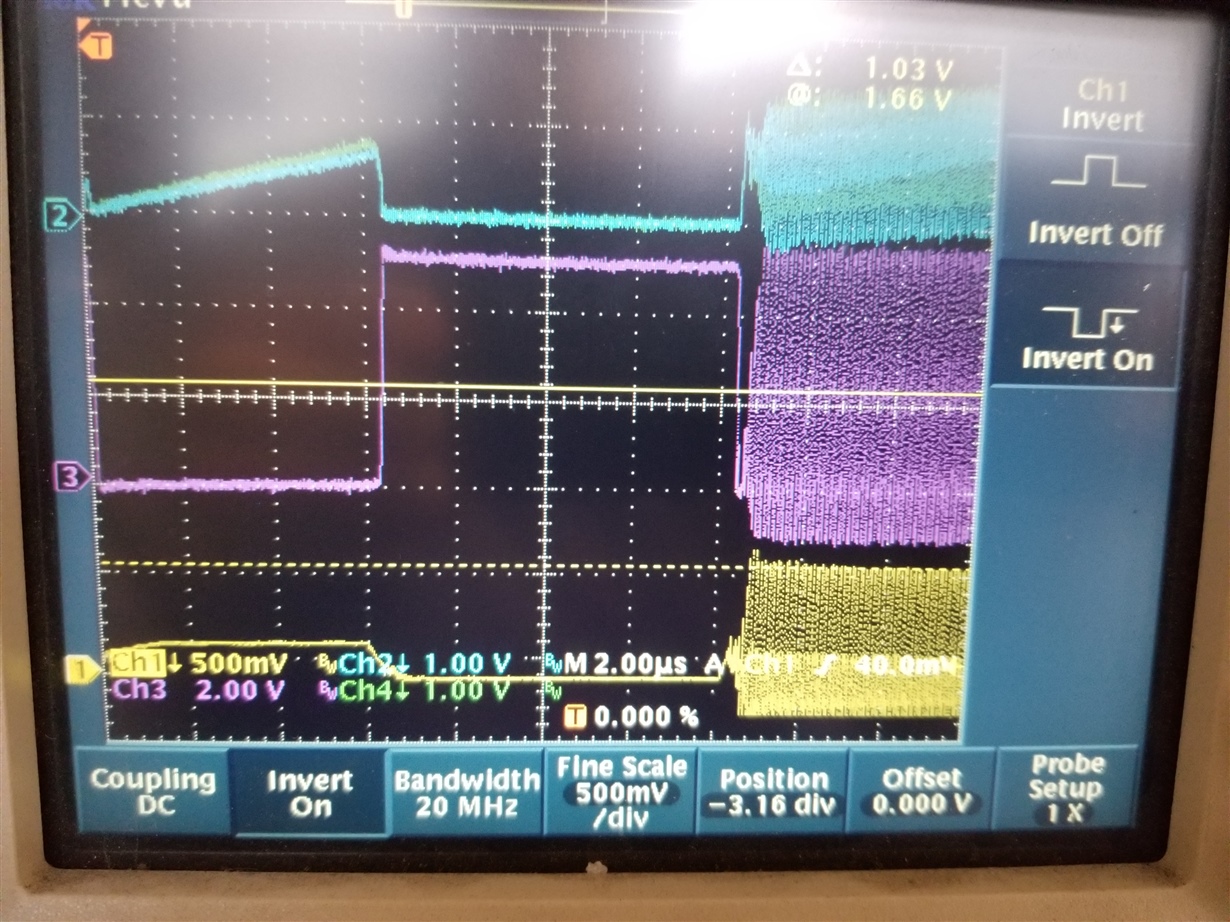

Green/Blue - Rogowski coils around the high-side drain of each paralleled SiC module - these show pretty good balance between the two at the lower currents. Scale is 10mV/A

Purple - high-side drain to source waveform - scale is 1:100, our drive voltage is 18V/-5V

Yellow - high-side gate to source of one of the paralleled SiC modules. Scale is 1:100, this is on a 500V bus

The UCC21750 is definitely not capable of driving at the frequencies (or voltages) seen to the left, so we are suspecting this has something to do with our gate loop or current buffer. On an event like the above the UCC21750 gate driver is destroyed. The 33MHz may be in the ballpark of the rise/fall times of the BJTs driving the actual gates, however, so there is some suspicion that noise is coupling into the base of the BJTs which have something like a 200% CTR and could be amplifying the noise.

Here's an image of the board to get an idea of the gate loop layout - since the CAS325 modules are facing each other, the paralleled gates are diagonal from each other so the loops need to somewhat wrap around each other to reach the desired gate

I know this is not an issue directly related to the UCC21750 but wanted to throw this out there to see if anyone with high voltage/high current switching experience has any knee-jerk reactions to what we're seeing here.

Any speculation is appreciated!