Hi Tier,

I have a question when testing the VDS stress of CSD95485 and would like to ask.

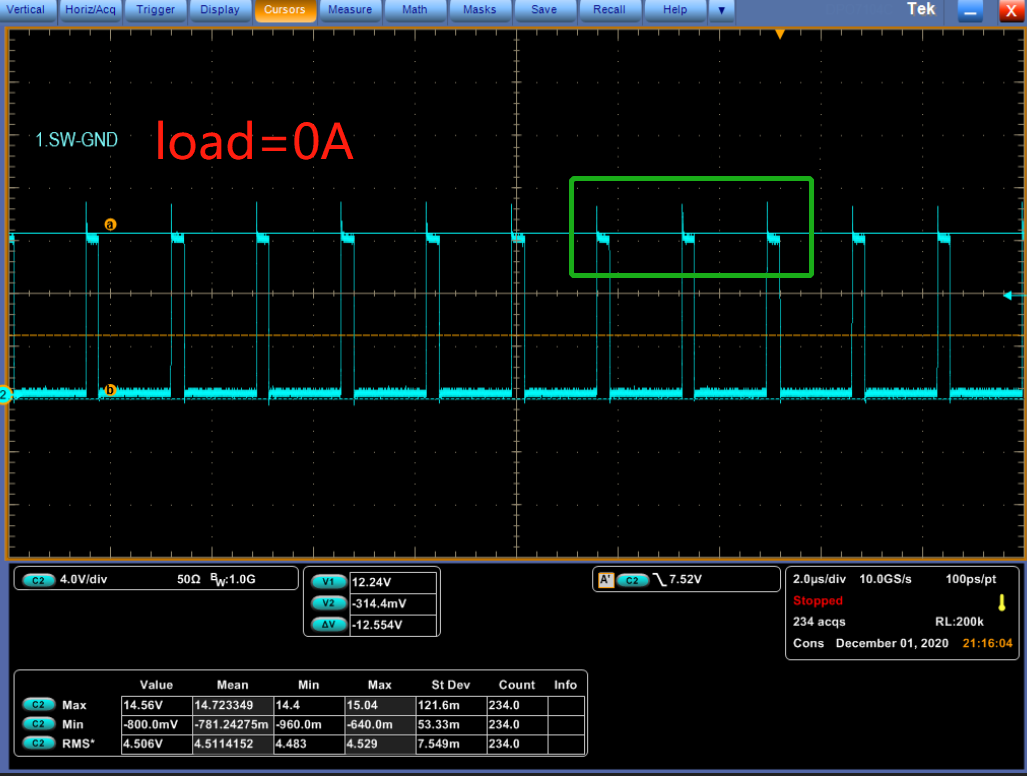

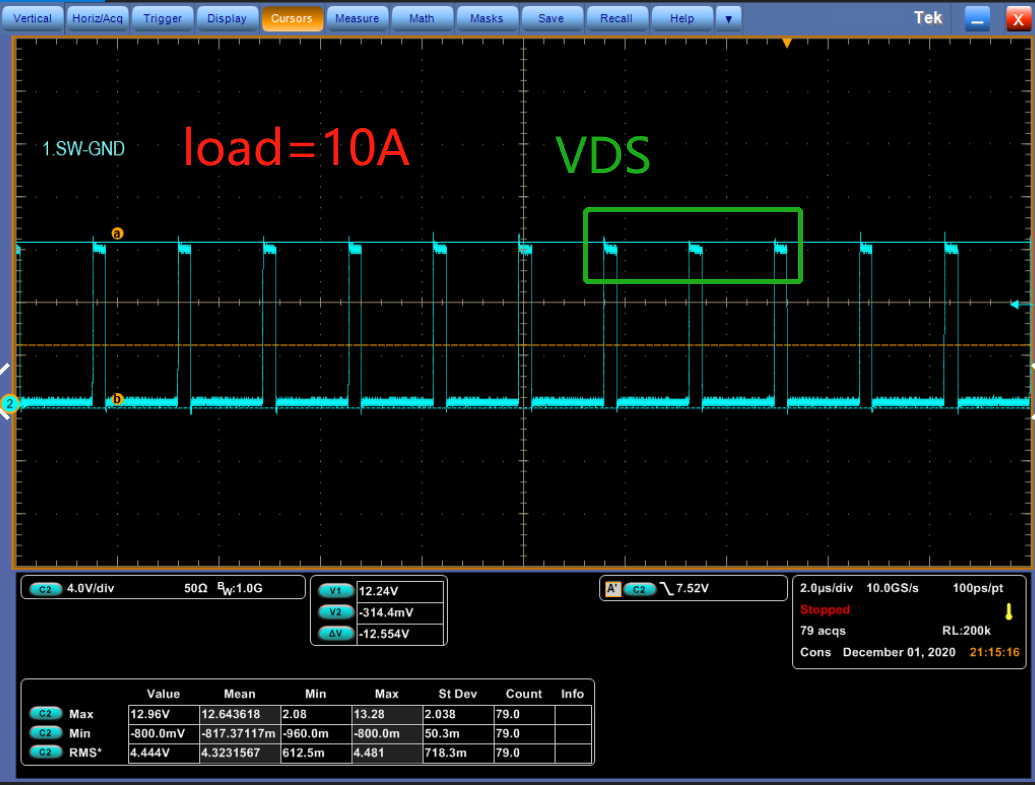

When load=0A, the VDS waveform seems normal, but when the load is 10A and load=10A, Why there is no peak voltage in the measured waveform? normally, the peak voltage increase with load rise, since the parasitic inductance.

The waveform is as follows, thank you. PS: Test environment, oscilloscope is Tektronix DPO7104C. Differential probe TDP1000_42V_1GHZ. The R-C of BOOT-PHASE is 2.2Ω, 0.22uF.