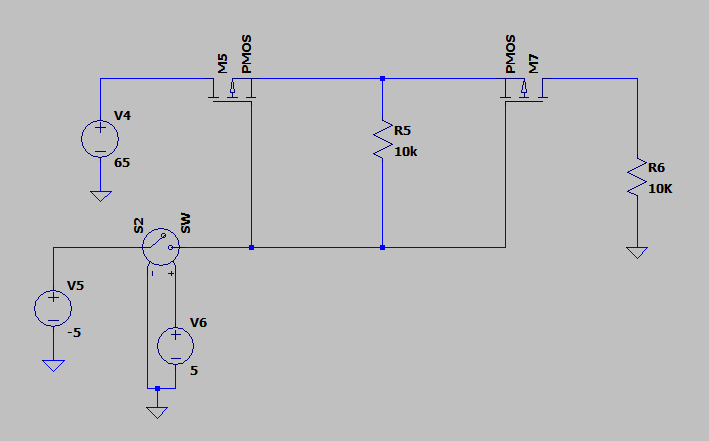

I am planning to do a switching circuit by using back to back P-MOSFETs

Switching Voltage - 0.8VDC to 65VDC

Switching Current - 0.8V/3A and 65/12A

I am using a negative voltage supply to drive the MOSFET.

When Vin 65VDC and the MOSFETs are in OFF condition the VGS will be nearly 65VDC at the same time this 65V will appear on the output of the Negative voltage regulator (There will be a resistor (1k~10k) between source and gate ).

Whether it will cause any damage to the negative voltage supply? (Negative supply will be in shutdown mode, we have control over there)

Suggest some solution for this.