Other Parts Discussed in Thread: STRIKE

Hello Sir:

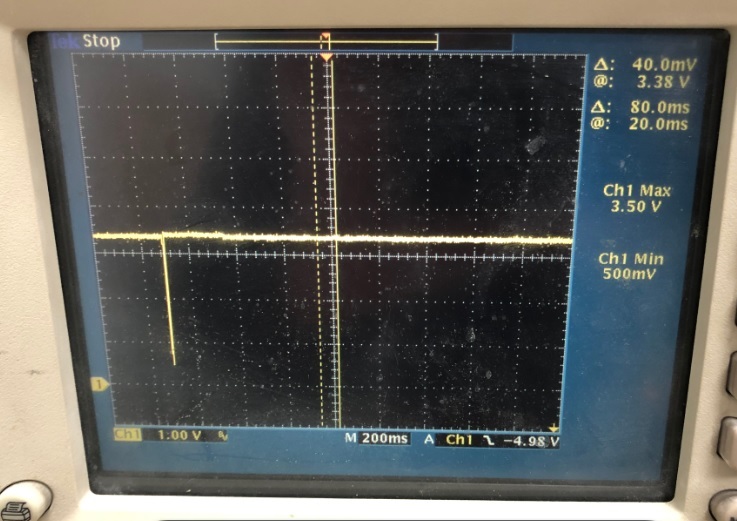

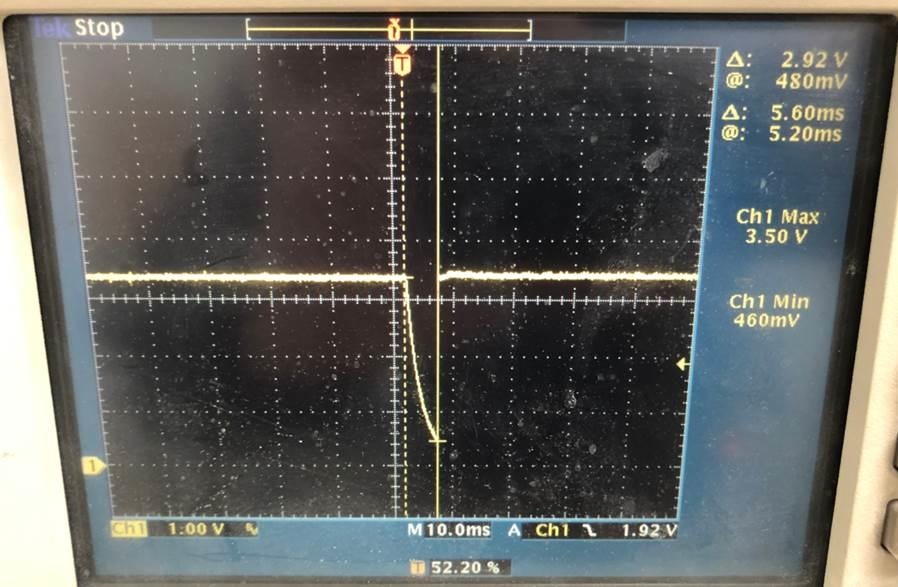

We are testing ESD contact +/- 8KV on Pack+.

Wehn using +8KV on Pack+ we found out that REG1 has dropping 460mv. (We setup REG1 to 3.3V)

Please refer the figure as below.

Can you provide recommendations for us how to fix this issue?

If you need schematic or gerber file please provide your email for me.

I will sent it for you.

Thanks a lot.