Hi Team

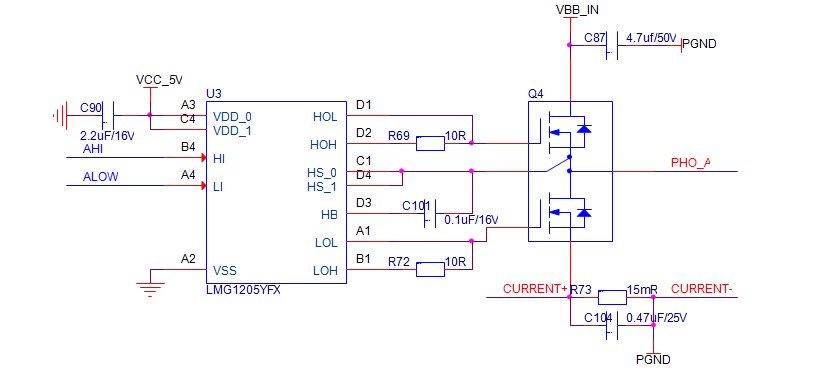

When we use the LMG1205 chip, when the ambient temperature is 80℃, the upper bridge arm will be out of control and always output high level. We used 200+ pieces of products to do the test with an ambient temperature of 85℃, and 14 pieces had problems. , After the normal temperature is restored, there are two problems that persist. The remaining 12 blocks will disappear after the normal temperature is restored, but they will recur after heating. We have used this chip for two years and there has been no problem. The problem suddenly appeared in this batch recently, so we suspect the quality of the chip. At high temperatures, the input waveform is normal, the power supply voltage of LMG1205 is normal, and the subsequent MOS is also normal. I did an experiment to make the input level of LMG1205 constant low (with a pull-down resistor), and there will still be a fault that the upper bridge arm becomes higher after a high temperature.

Thanks.

Best regards,

Chase