Hi Expert,

BQ76200 is used on customer side. The schematic is same as the reference design:

It's the second for customer to use this device, the schematic for two project is same. But the layout is different.

For the good one, 470nF(for Charger Pump part) is far away from 10MΩ resistor(for CHG output), it can work well when the CP_EN and CHG_EN enable at the same time;

For the issue one, 470nF(for Charger Pump part) is close to 10MΩ resistor(for CHG output), it can't work well when the CP_EN and CHG_EN enable at the same time;

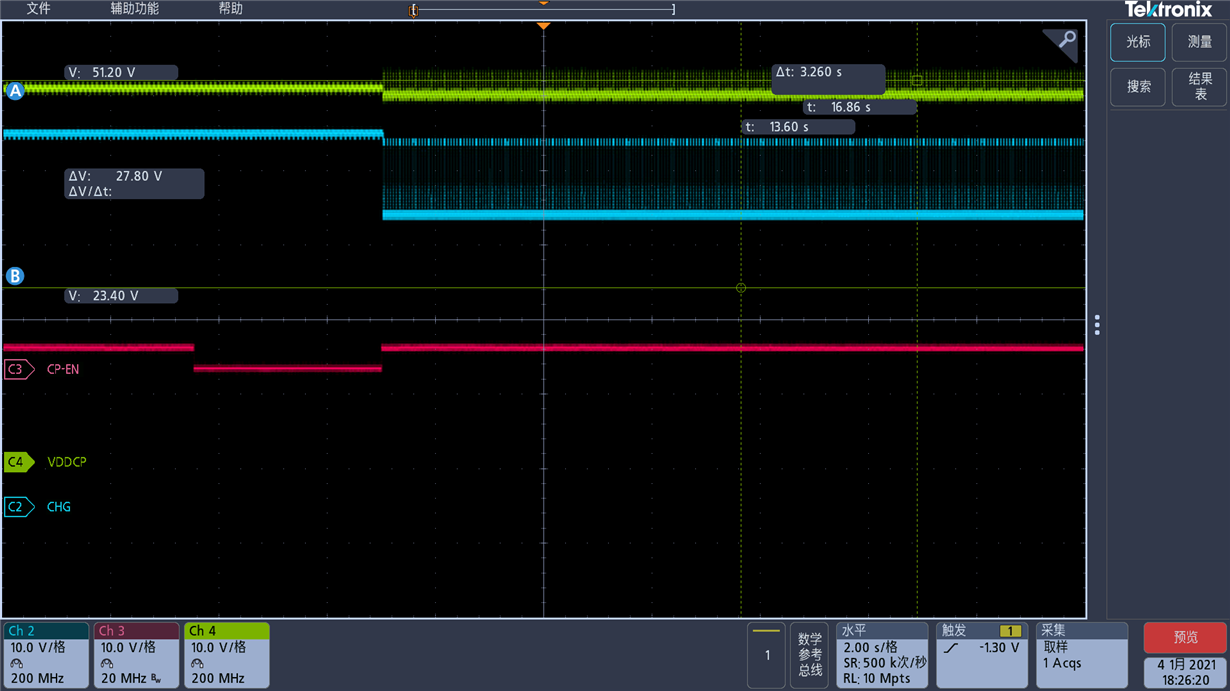

When they enable the CP_EN, CHG_EN Pin Enable at the same time. CHG output wrong signal. See the screenshot for waveform:

CHG_EN is follow CP_EN, it doesn't show in this screenshot:

Support need:

1. could you comment on this issue? Which part can cause this kind of issue?

2. Any suggestion for layout of 470nF(for Charger Pump part) capacitor and 10MΩ resistor(for CHG output),

Best Regards

Songzhen