Other Parts Discussed in Thread: BQSTUDIO

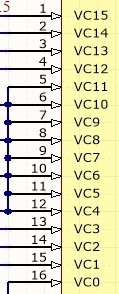

We are using a custom board with 20 ohm resistance in series between BQ and cell terminal. A six cell battery is connected to BQ with the following connections:

VC0: GND

VC1: Cell 1

VC2: Cell 2

VC3: Cell 3

VC4-VC5: Cell 4

VC6-VC15: Cell 5

VC16: Cell 6

When we write to the CB_ACTIVE_CELLS register and read it back, it's what we expect when we're either clearing it or setting any of the first three cells to balance. However, when we try to set other bits, and read them back, we get 0x00. We can also use CBSTATUS2 and CBSTATUS3 to .verify that our loop successfully continues to activate balancing on. Cells 1, 2, and 3 (and we can see a voltage across their corresponding balance resistors), however, none of the other cells have apparently been balanced for any amount of time. We've also verified that the cell temperature reading is well within the default limits.