Other Parts Discussed in Thread: TDA4VM, TPS22965

Hi team,

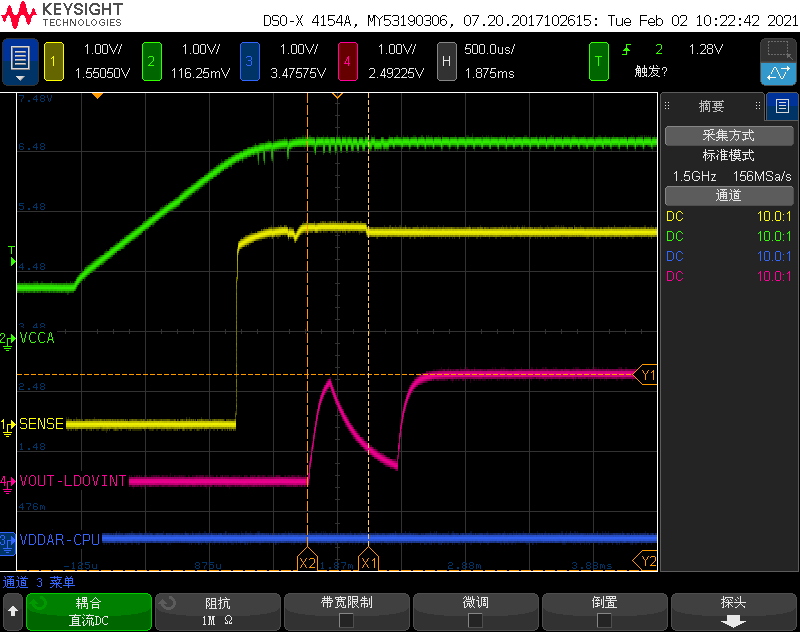

My customer is using TPS659411 and TPS659413 to power TDA4VM, but they fail to power up the device (buck and LDO1-4) randomly.

Could you let me know the possible reasons? And how to debug next?

Please find test waveforms and register reading in attached, thanks.

Dongbao