Hi,

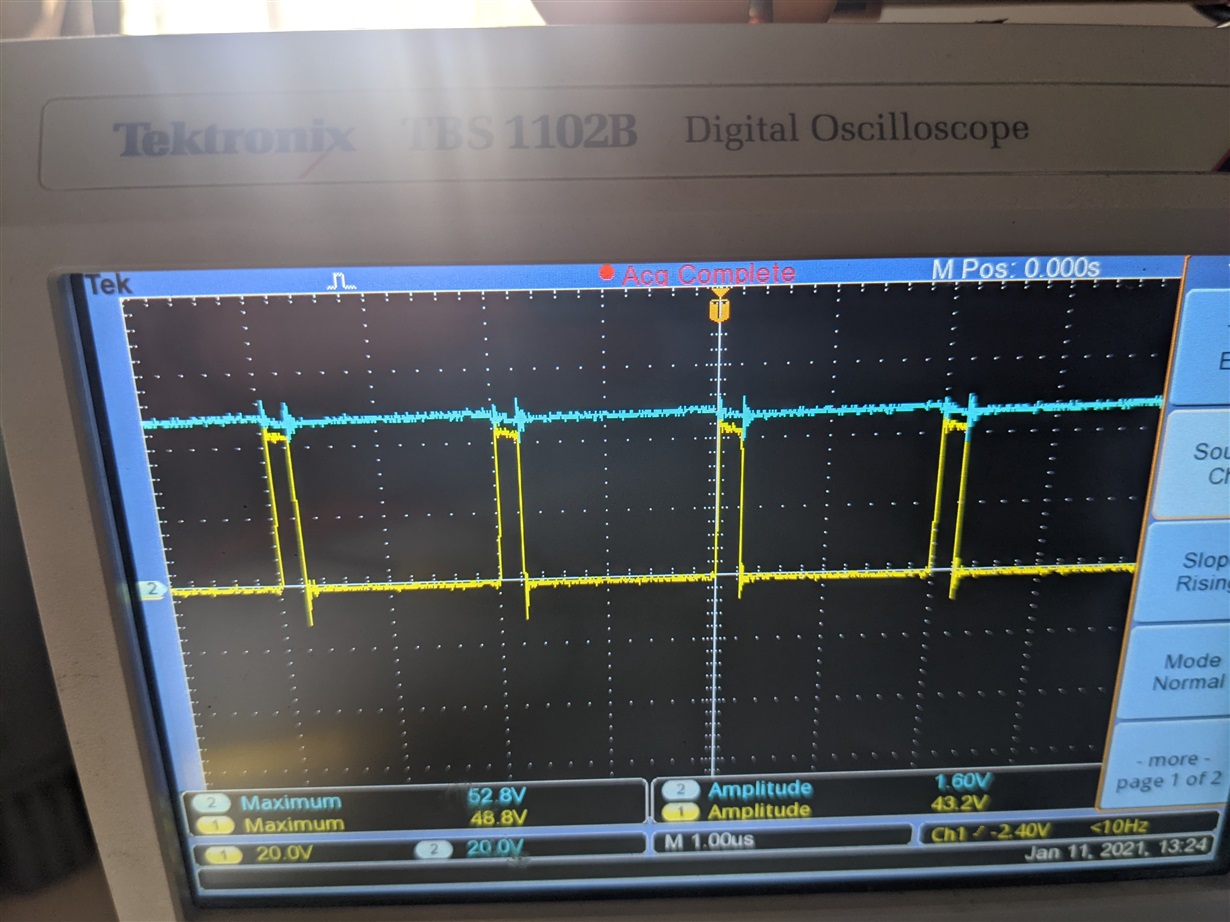

I am using Lm5146-Q1 to run DC Motors with a motor driver. The LM5146-Q1 is connected to a battery with a nominal voltage of 48V. The Buck works fine for most of my cases but in cases where my motor has to start and stop within seconds, my high side MOSFET fails (CSD19533Q5AT).

The issue leads to the motor driver seeing the battery voltage which leads to other failures. It would be great if you can help me with the issue.