hi sir

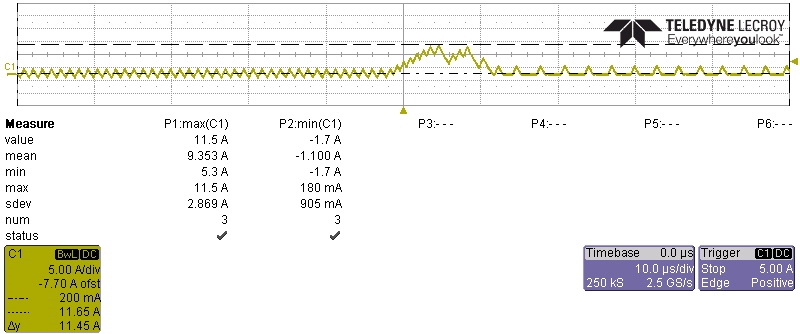

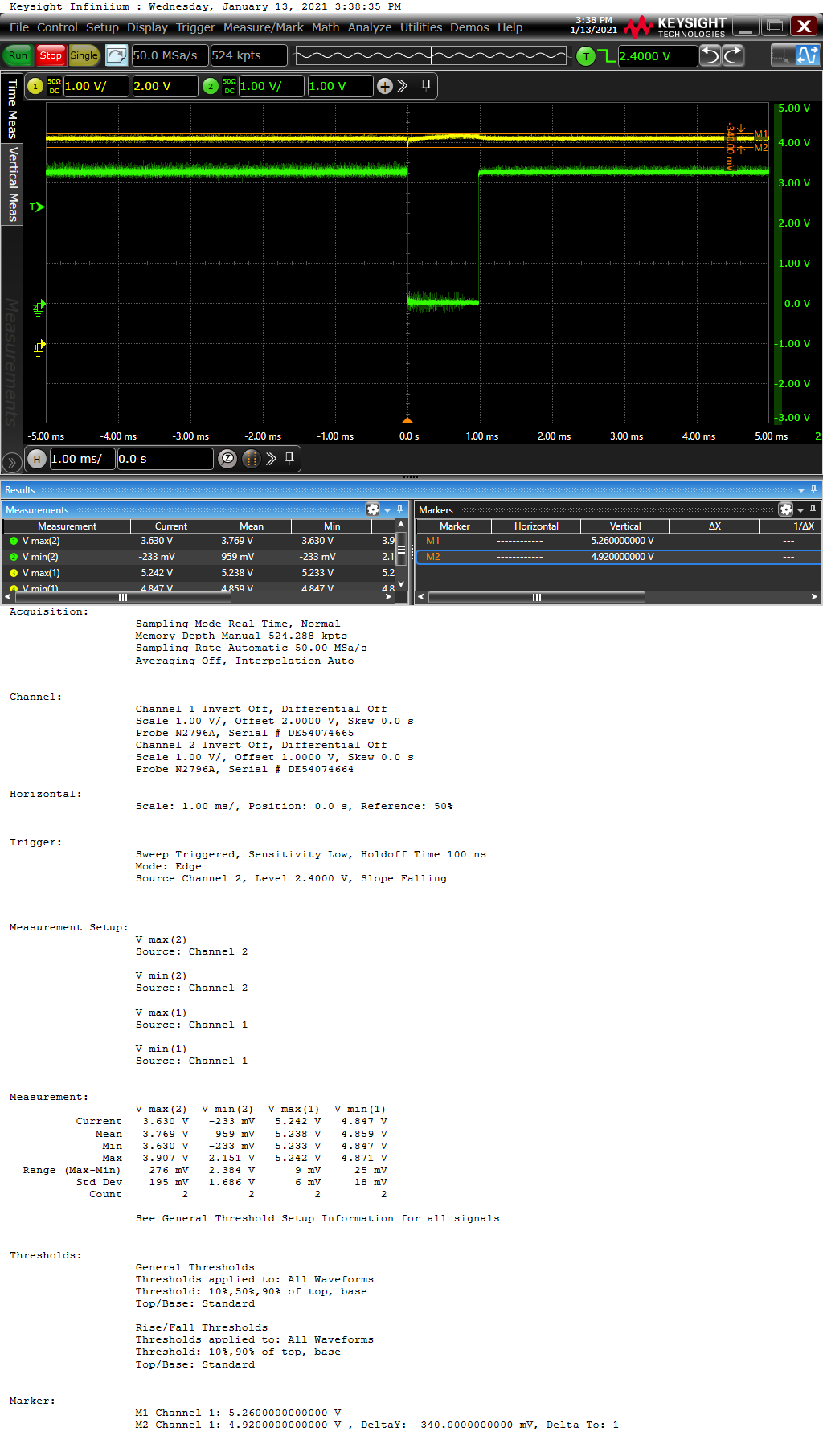

i'm using tps53319 to convert 12V downto 5V in my board,when the board is inserted a usb CD driver,the powergood signal of tps53319 is pull down a little while and then go high,i have measured the current and voltage of tps53319 when the USB CD driver is inserted,i don't think the current is high enough and the voltage is low enough to pull PG down,the next 2 picture namly current and voltage, signal PG i have tested.

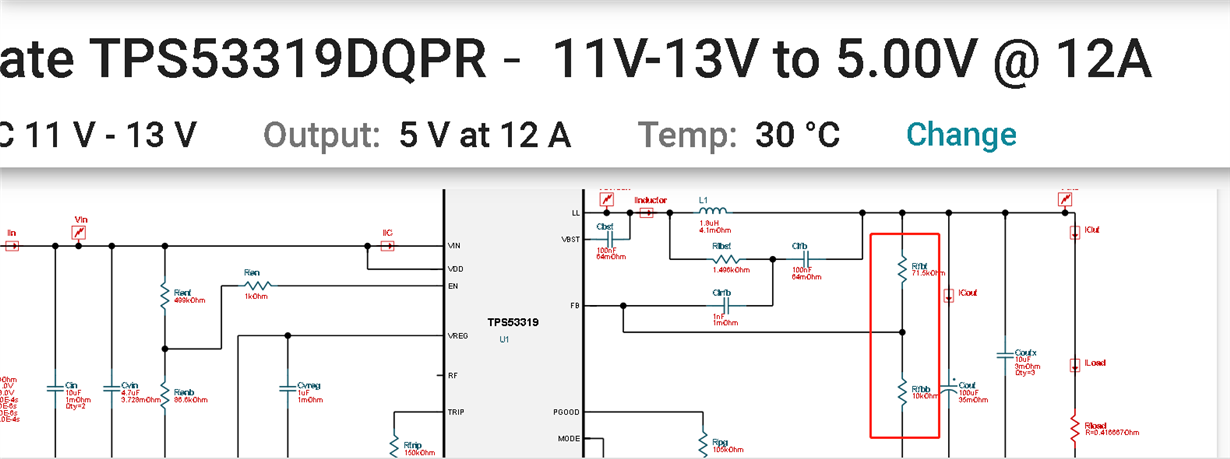

my design is next picture

Looking forward to your reply