Hello,

I have a TLC6946 driver in a 1:4 multiplex.

1. my problem is that the datasheet is a little unclear. In the Technical Reference Sheet it says that I should use 310 GCLK during a sub-period. But during a sub-period I also have to switch through all 4 lines with external MosFETs or?

How many GCLKs do I have to use while showing one line on the display?

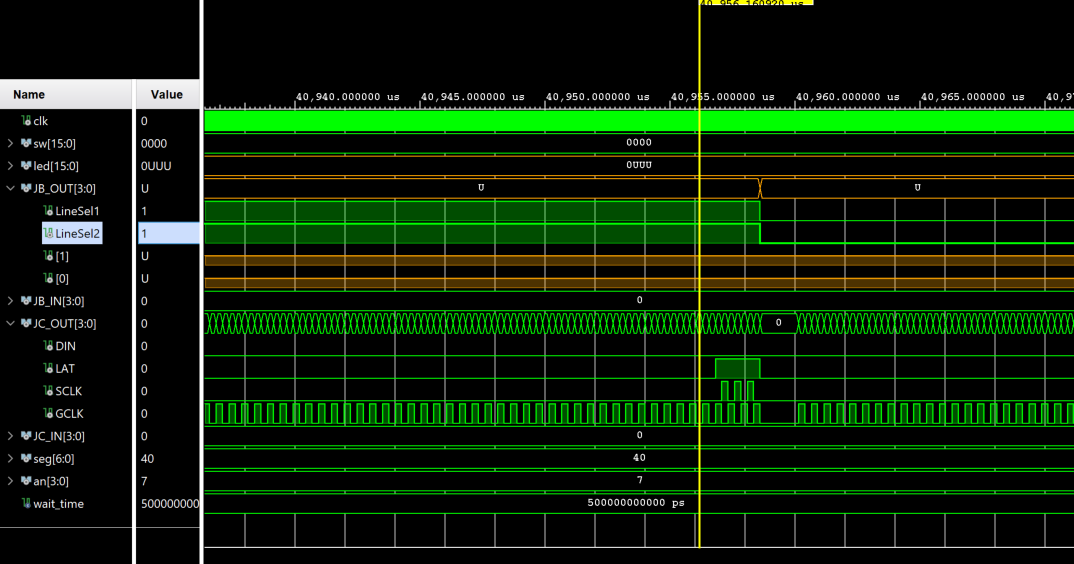

2. when and how do I send the VSync command? Currently I send it, during the last sub-period, before switching (see screenshot). Is this correct or do I need to have GCLK pause first? Do I need to be able to turn off the lines completely externally? (I can control with 2 bits the four lines, so one is always on...)

Thank you very much for your answer.

Kind regards,

MIchael Brandmaier

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.