Other Parts Discussed in Thread: CSD17581Q5A

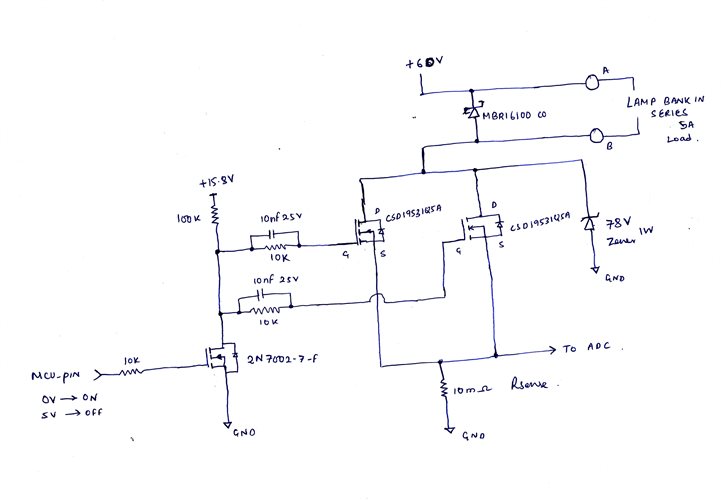

Problem:

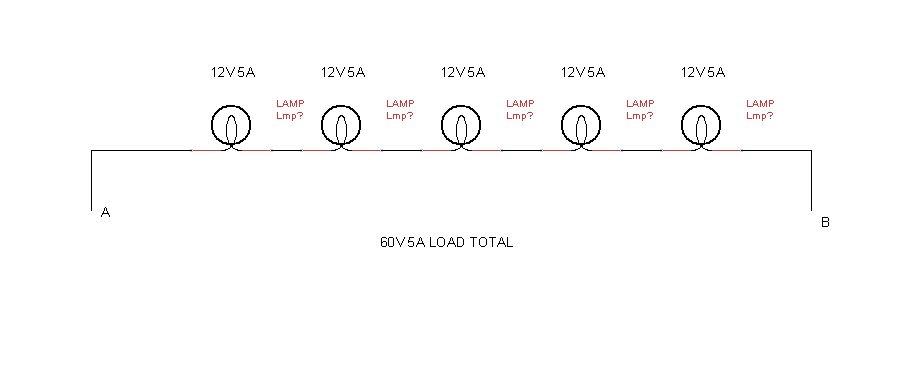

CSD19531Q5A Drain and source pins were showing short. When we unsolder and solder back, no issue. This happened 3 out of 5 times. The soldering was done by hand.

1. Please let us know what could had caused the short with drain and source?

2. Does ESD or charge accumulation has anything to do with it? or is it purely soldering issue?

Thanks & Regards,

Macjan.