Other Parts Discussed in Thread: TIDA-00449

I have been developing host driver for the bq76940 AFE module, I have listed the queries or doubts below,

1.As per the datasheet, we can set a fixed delay and thresholds for each faults supported by AFE, Once the Fault is detected corresponding Bit will be set in the SYS_STATUS register and alert interrupt will be generated, how the host knows the particular fault is cleared?

2.As per my understanding, once the host is interrupted with the fault let's say OCD fault, host will clear the OCD status bit, host has to poll AFE with a period greater than the OCD delay and reads the OCD status bit, if the bit is not set then host understands the fault is cleared, Is my understanding correct?

3.In order to clear a bit in SYS_STATUS register, we need set the bit with 1 , which inturn clears the bit in SYS_STATUS register. Is my understanding correct?

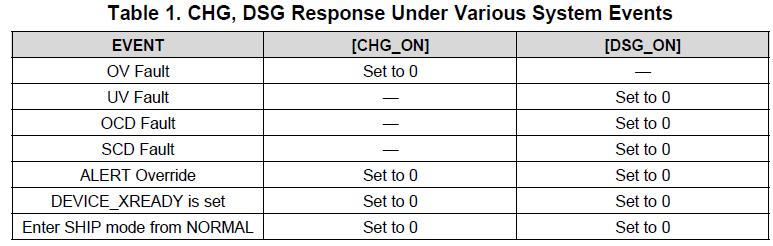

4.Once the AFE detects a fault, immediately AFE sets the state of DSG and CHG mosfet as per below table without the interventions of the host controller?

5. In order to exit from ship mode to normal mode, voltage greater than Vboot is applied for a period greater than Tbootmax on the TS1pin, After Tbootmax , voltage on TS1 pin can go to zero it will not affect the boot sequence, Is my understanding correct?

6.In the middle of a normal operation, suddenly host undergoes a software reset then how the host knows the afe mode whether it is in ship mode or normal mode?