Hi All,

I would like to ask a question on TPS54310 connection.

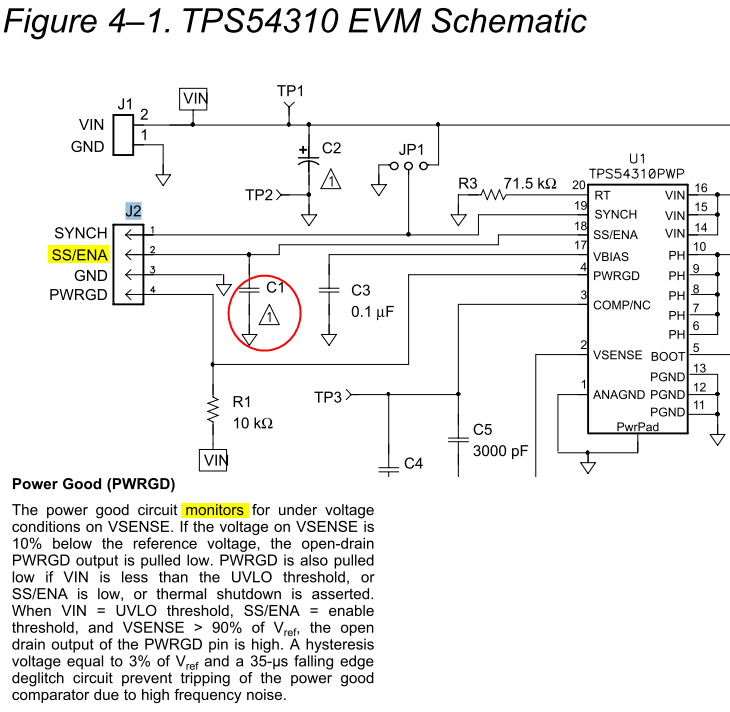

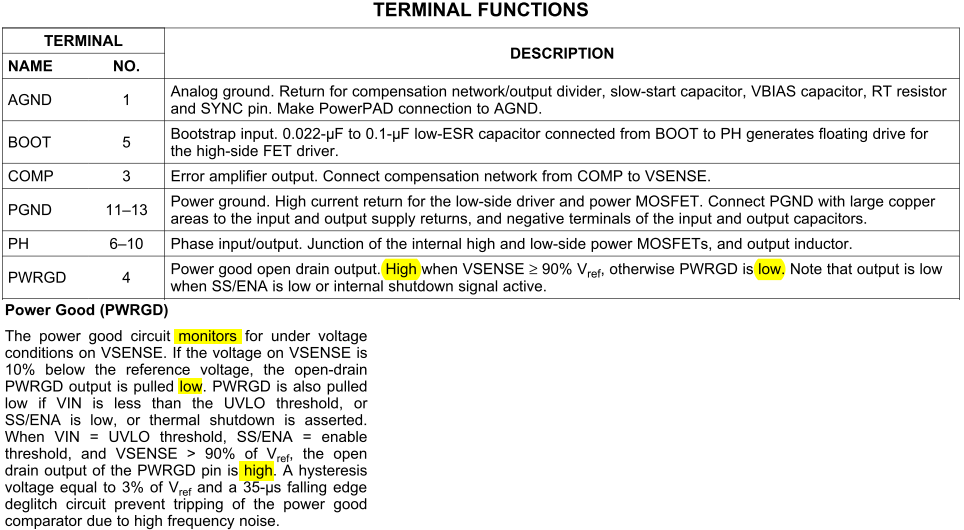

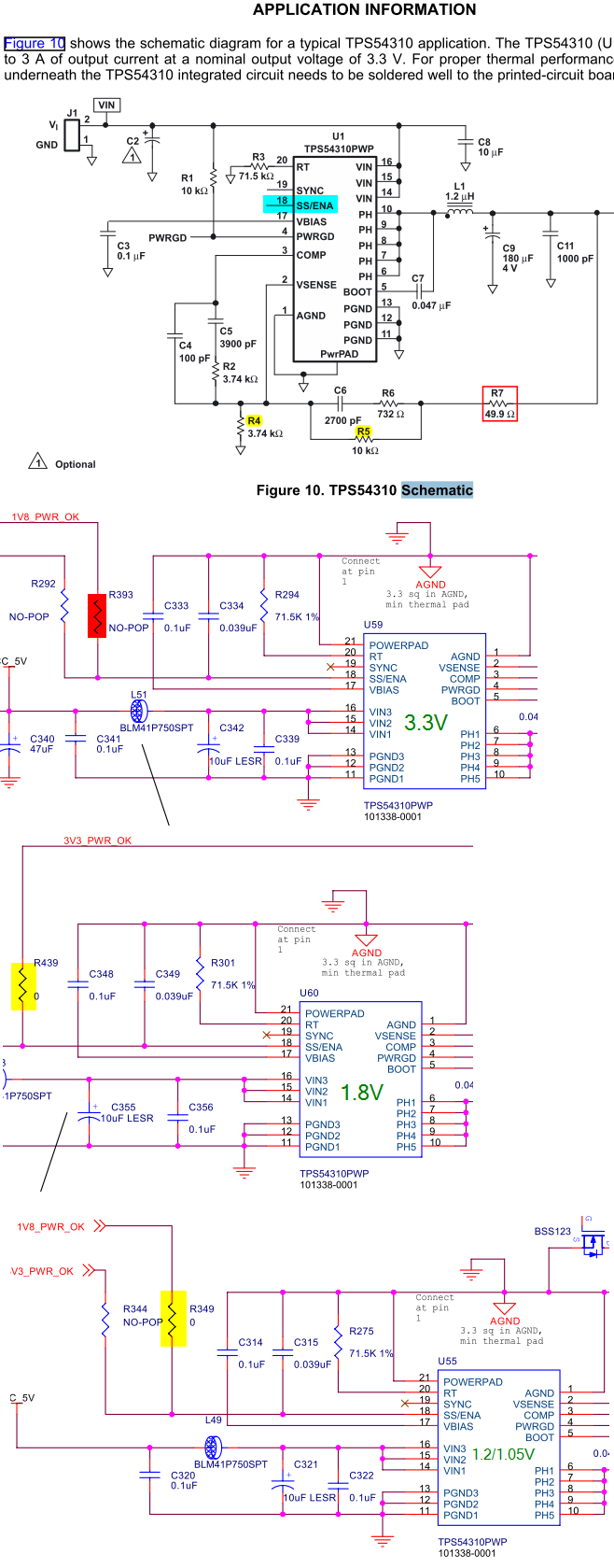

In the schematic shown in SLVS412d, the pin is unconnected. However, on EVM6437 which I am referencing, I found that the pin is connected on one TPS54310 and unconnected on another two:

1. For TPS54310 output 3.3V, the pin is unconnected.

2. For TPS54310 output 1.8V, the pin connected to 3.3V.

3. For TPS54310 output 1.2/1.05V, the pin connected to 1.8V.

There seems to be some regularity here that regulators output lower voltage have their SS/ENA pins connected to regulators output higher voltage, in a cascading manner.

But why? Are they necessary? If I left all SS/ENA unconnected, will the system work?

I went to page 12 (Slow-Start/Enable) for its detailed description, and there seem to be related to threshold issue. My guess on its purpose is that:

1. By cascading higher voltage output to lower voltage output regulator’s SS/ENA pin, then power will be distributed to board devices in the same order, during the short time when the 5V supply is plugged in.

2. This should be related to either

a. Booting

b. Reset

procedure.

Is this true?

Anyway, the most important question here is on their necessity. Do I have to connect SS/ENA in that cascading fashion to be able to use my board?

Thanks,

Zheng