Hi

Could you please let me know the dead time between high side FET off and low side FET on, and Low side FET off and high side FET on?

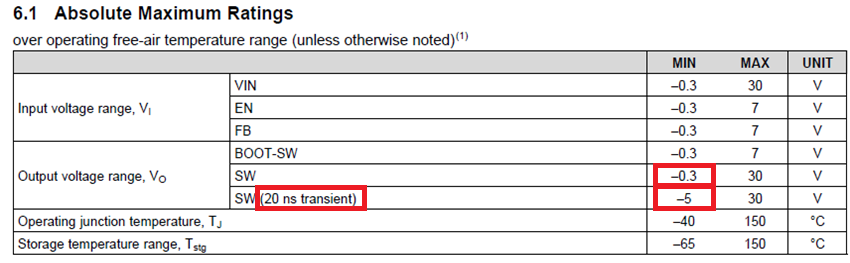

Negative voltage(around -0.6V) on SW node during dead time was measured over 50ns(absolute max, transient time) .

I think, those negative voltage are internal operation during dead time. so it is no problem because it is not external apply voltage. is it correct?

Also, is the dead time on the waveform normal?

Thanks

Muk