Hi Team,

Our team is using BQ76940 to develop products, and we have some problems in battery balancing and need help from you.

In the 1-5 group, the 1 3 5 cell balance is turned on at the same time, and the 5 cell balance cannot be turned on. The same is true in the 6-10 group.But it is feasible to turn on each one separately

This is related to our balanced circuit diagram.

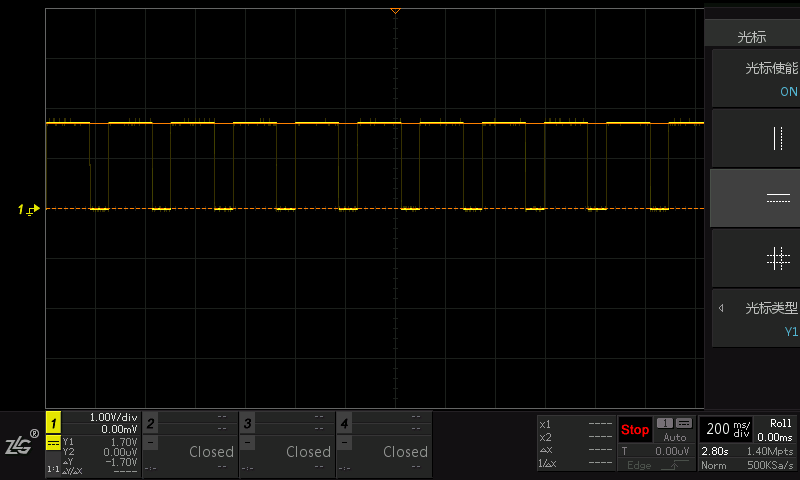

We measured the gate of the N-MOS with an oscilloscope yesterday, and we got the following waveform when the 5 cell were individually balanced

The time occupied by his high level and low level is in accordance with the specification, the total period of 250ms, 175ms balanced time 70%.

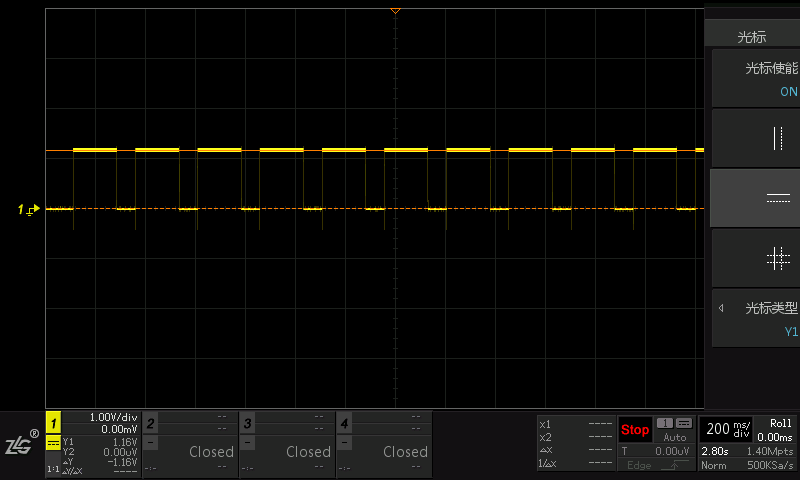

You can turn on the balance of the 3 and 5 batteries at the same time. This is their waveform, and the time period is correct, but the voltage drops to 1.2v.

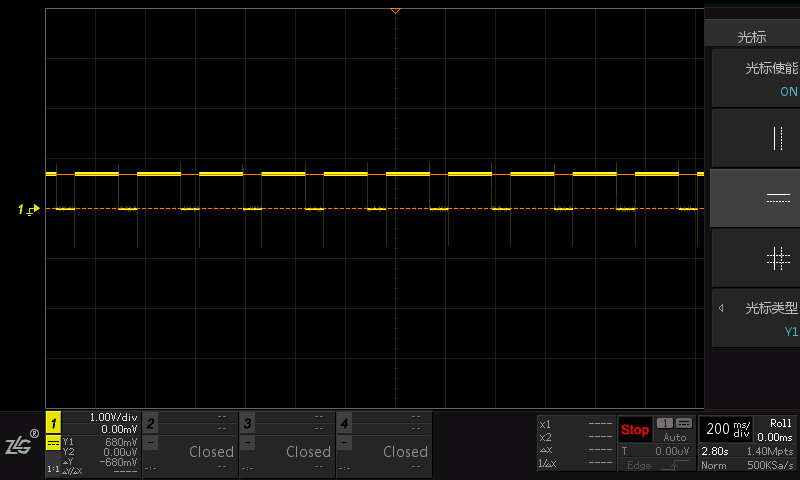

But when we turn on the balance of 1 3 5 batteries at the same time, 1 3 can work normally, and 5 cannot. The following is the waveform diagram of No. 5 at this time, the time period is correct, but the voltage has dropped to 0.7v, this voltage can no longer make the N-MOS tube turn on.

In the data sheet, we only see that two adjacent batteries should not be balanced together, and there is no explanation for how many are turned on at the same time. Whether only two batteries are allowed to be balanced in each group of 1-5, 6-10, 11-15 , Or because of the problem of our equalization circuit, the output capacity of the chip is reduced.

Expect for your kindly reply, thanks.

Best Regards