Hi,

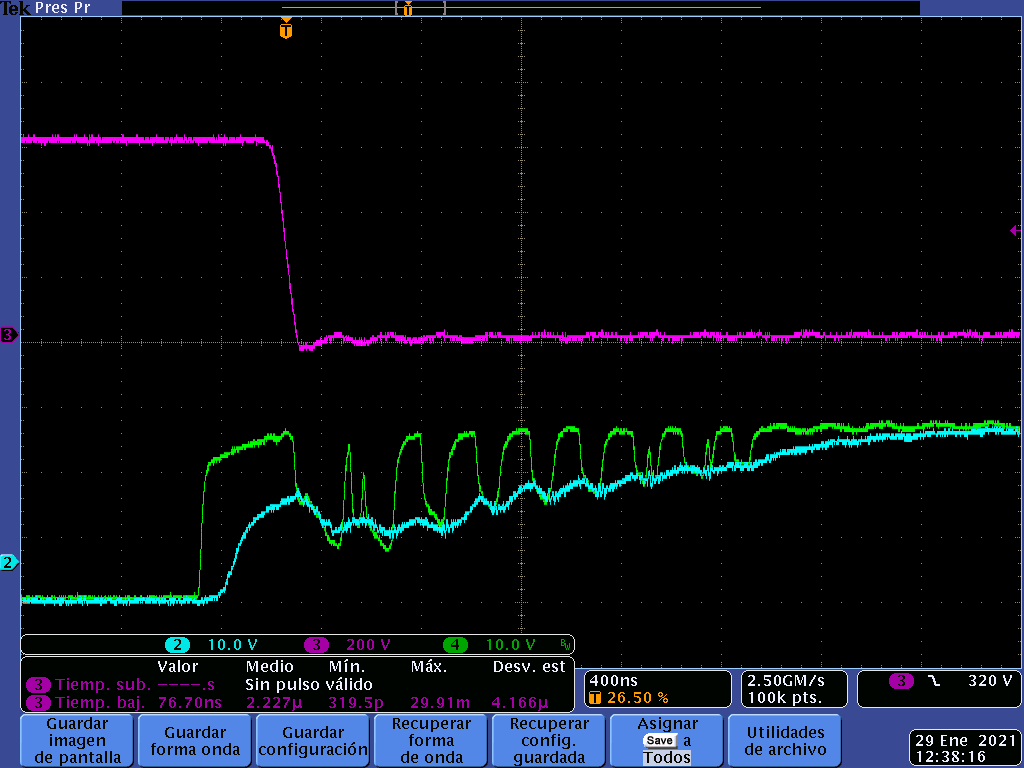

I am currently workin in a 250kW SiC inverter using the UCC21750 to driver the SiC Modules. In some occasions (ramdomly) we see a gitch in the ouput of OUTH and OUTL which turn on and off the MOSFET. At the beginning we thougth it was caused by the parasitic current flowing through Cgd due to the dvdt, but now we have changed our mind and we think it is caused by the driver since it is the OUTH and OUTL which are pulling down or pulling or up the gate signal with high frecuency oscillations.

We also see the same effect in the followin simulation. To avoid this high frecuency oscillations we could increase the Cgs with an external capacitor (330nF) but this would increase the power required to drive the driver and we are not allowed.

Any idea where this effect is coming from?

Thanks in advance