Hello,

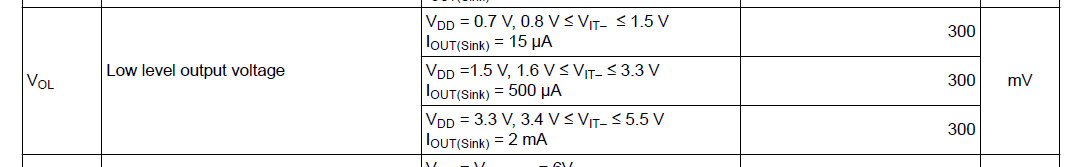

I have a question about V_OL specification of TLV840.

Usually Reset IC has to keep LOW signal during all VDD range less than V_IT+/-.

For example, when using Vth=2.8V, it has to keep LOW output from around 0V to 2.8V (I know it actually has V_POR).

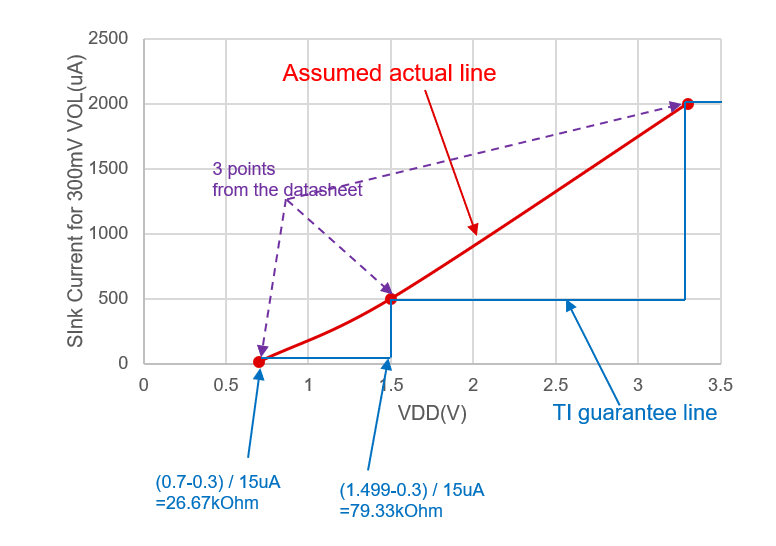

So From this specification table, to keep VOL under 300mV from all 0 ~ 2.8V range, I think I_out(sink) have to be less than 15us from this table.

So I don’t think VDD=1.5V case and VDD=3.3V canse don’t have so much meaning.

For example using 10Kohm of pull-up for Vth=3.4V device, the sink current is

When VDD =3.3V, 3.3V/10KOhm = 330uA < 2mA. It's OK.

When VDD = 3.29V, 3.29V/10Kohm = 329uA < 500uA, It's OK.

When VDD = 1.49V, 1.49V/10Kohm = 149uA > 15uA, It's not OK. The reset output may be over 300mV from this specification table.

From this thought, if the user want to keep under 300mV from 0V to Vth, they have to use under 15uA condition from 0.7V to 1.49999V range.

Does this my understanding correct?

I feel this specification is a little bit strange.

Regards,

Oba