Hi TI Forum Team,

Currently I am working on BQ76942EVM TI Eval board. i am facing the below problem.

Problems :-

My problem is when I used the Cell simulator(or using jumper setting) between Cell1-Cell10 (between BAT- to BAT+).

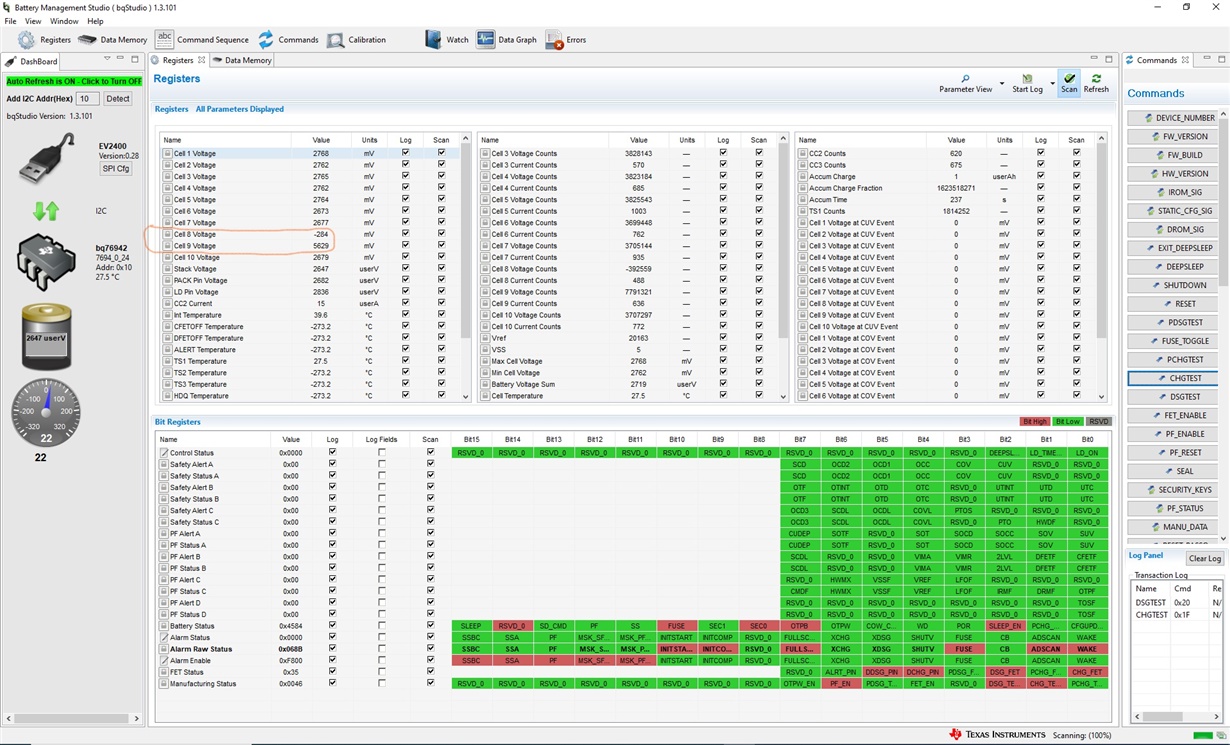

when we remove any one jumper to make voltage not equal between two conjunctive cell(Cell8 or Cell9) , the voltage appears on cell8 voltage and cell9 voltage is given and marked on the screen shot attached with this thread in more details. please refer "Register.jpg" file.

if the difference between Cell 8 and cell 9 is not as per our setting, then why the DSG and CGH MOSFET is getting on/off by using DSGTEST/CHGTEST command by GUI(Battery Management Studio) while voltage between these two sell is not as per actual settings?

however in actual way in that condition either DSG/CHG MOSFET should not getting in ON condition. it should be in OFF condition .

so what setting/Register settings, I need to do to getting automatically DSG/CHG MOSFET will get OFF when this condition will encountered?

Note:- Same things happens in case of actual battery connection when one cell voltage is far below than all others cells.

OUR Register Settings:- I have settings the bellow Registers setting to manage this conditions

1. Data Memory-->>Settings-->>Protection-->>Enabled Protections A

2. Data Memory-->>Settings-->>Protection-->>CHG FET Protections A

3. Data Memory-->>Settings-->>Protection-->>DSG FET Protections A

4. Data Memory-->>Protections: CUV [Threshold, Delay, Recovery hyst]

COV [Threshold, Delay, Recovery hyst]

Please see the all above details is screen shot attached with this thread.

Data Memory-->>Protections :COV/CUV settings

CHG FET Protection A settings