TI guys

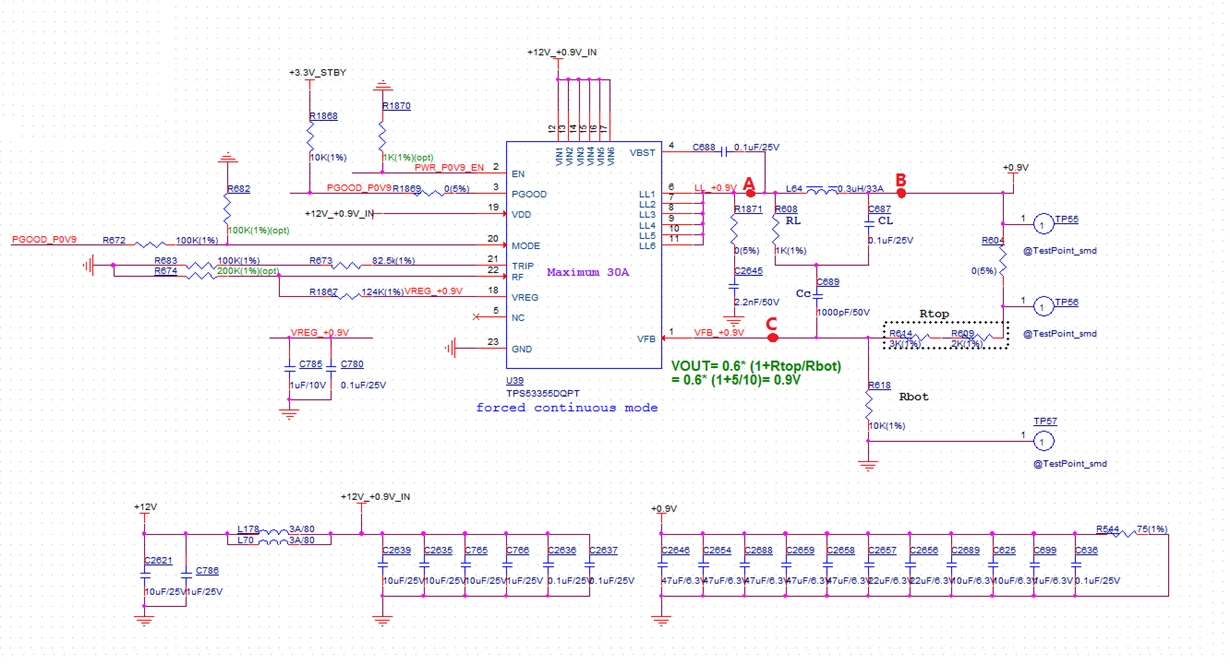

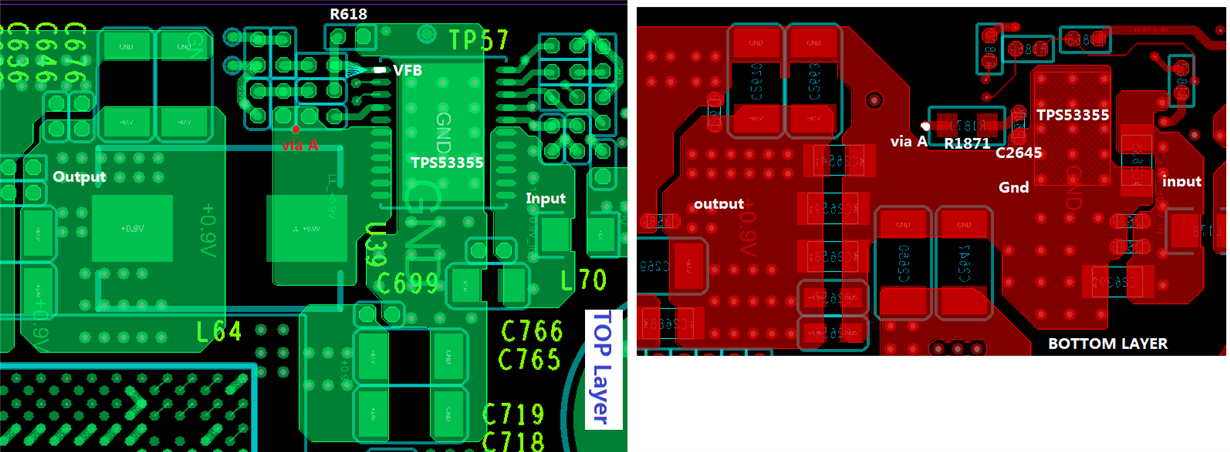

we meet a issue for TPS53355 design, refer to below pic for sch. the snubber circuit R1871=0,C2645=2.2nF.

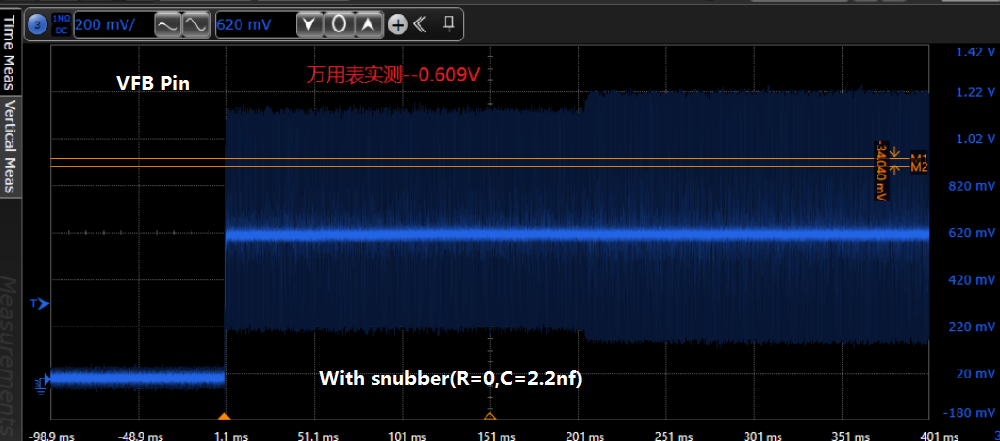

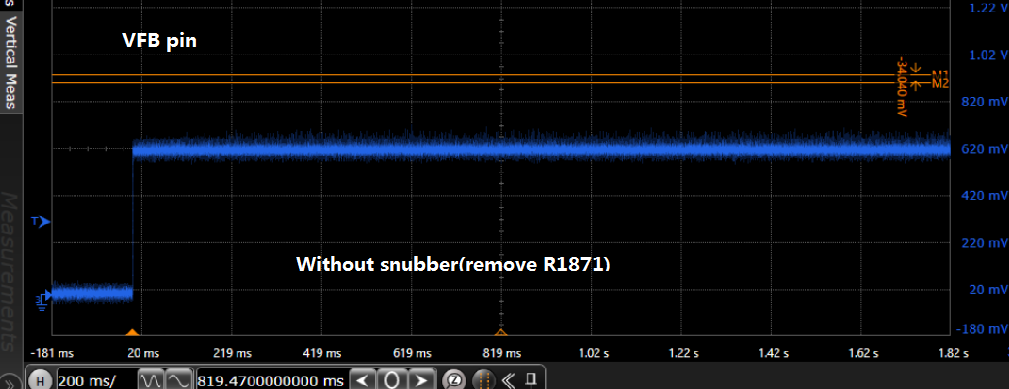

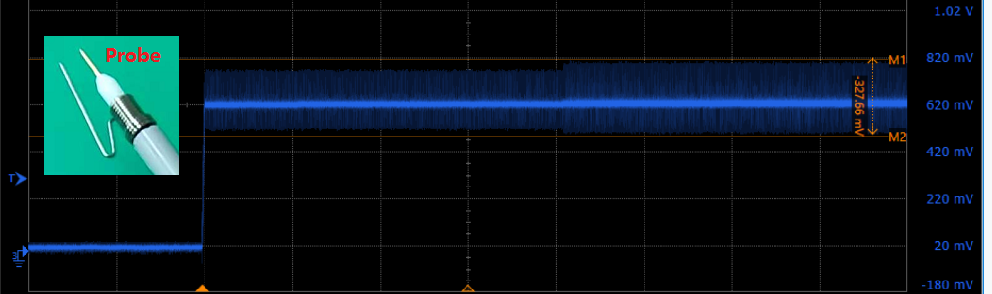

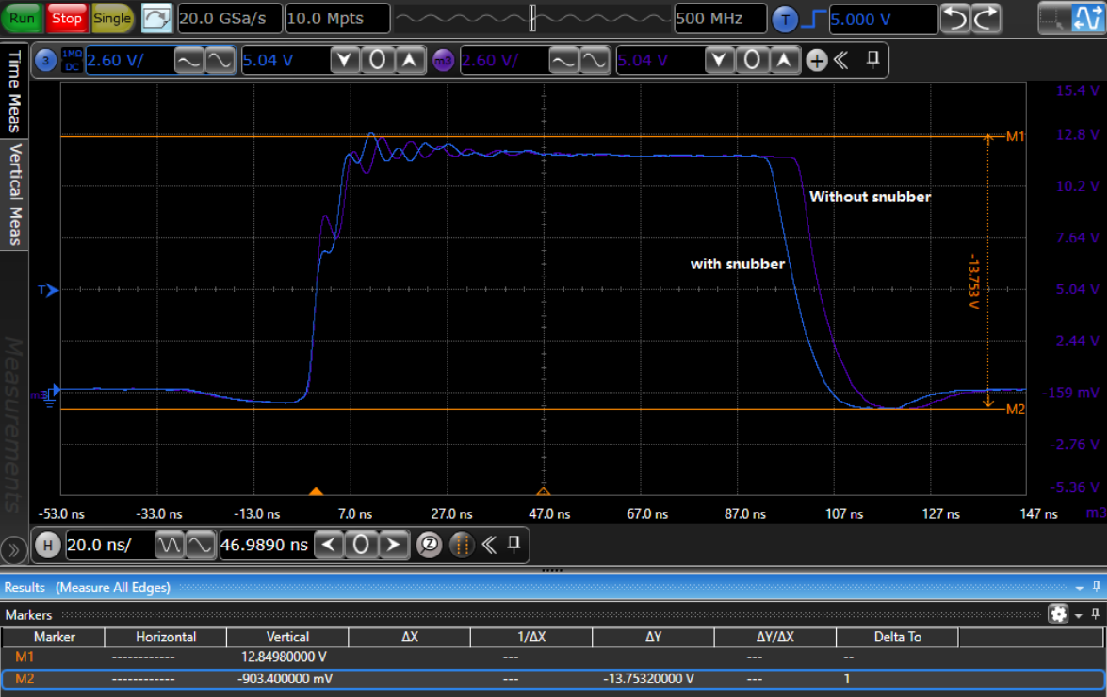

we test the waveform on the VFB pin(Point C) with and without snubber(remove R1871) separately.

we find the snubber will affect the VFB waveform largely.

Is it normal ? and how the snubber affect VFB ?

TKs.