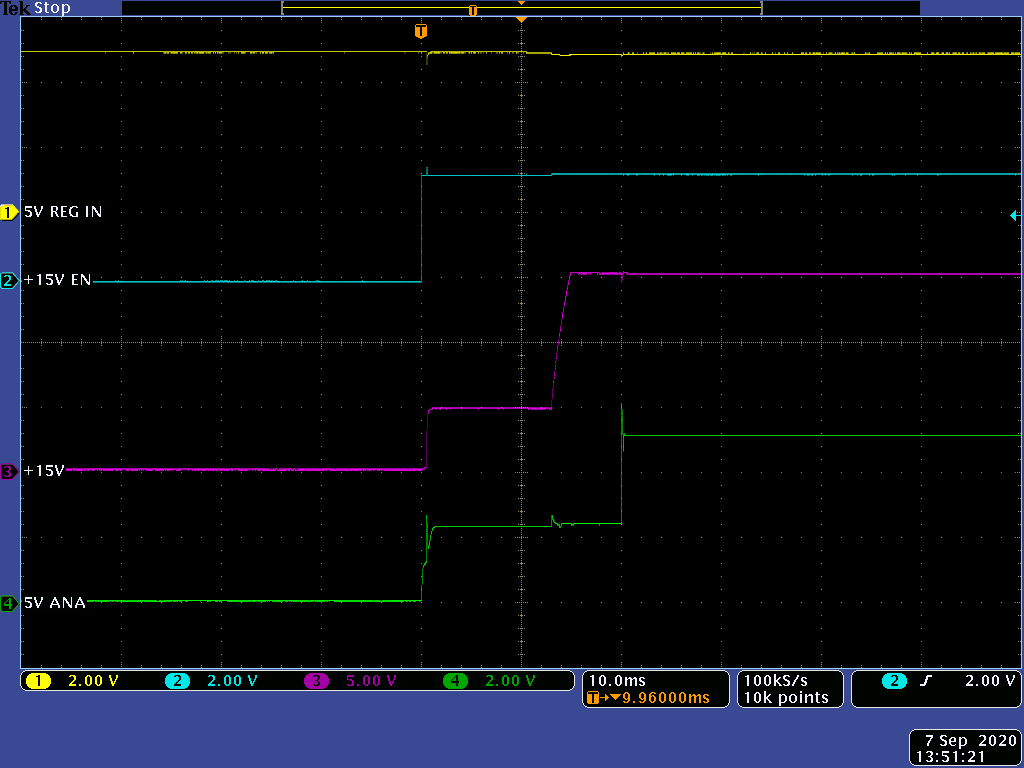

Hello, We have designed TPS65130 regulator circuit for +/-15V regulation. During power up we are seeing that -15V startup seems to be correct but +15V is not correct as we are seeing step from +5V after enable and after around 12ms +15V will be up. This is not the expected behavior and we need to solve this. Please can you guide /provide your suggestion as what could be causing this issue.

I have attached scope images for your reference. One is showing +/-15V startup and other showing 5V input to regulator, regulator enable, +15V and 5V LDO output connected to +15V output.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.