Hello,

I have some questions for Figure 81 on the datasheet of LMZM23600.

1.

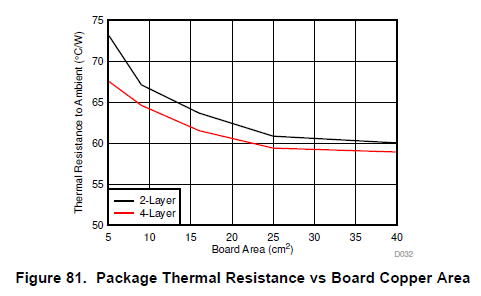

Is the vertical axis of graph, “Thermal Resistance to Ambient(C/W)”, the same as R_Theta_JA except for the board size environment?

R_Theta_JA is specified as 45C/W on page 5.

I know the thermal resistance to ambient highly depends on the environment. And the board size is one of big factors

But I feel that the values on Figure 81 are a little bit difference from R_Theta_JA, 45C/W.

So I want to confirm what Figure 81 shows.

2.

I would like to confirm where is Tj in this device.

Does “Tj” mean silicon die temperature inside this module like other usual ICs?

Regards

Oba