Other Parts Discussed in Thread: UCC28070

Hi,

Please suggest what type/model of to be used for PFC choke to achieve >92% efficiency.

Details enclosed for reference.

WBDesign16_390Vdc@9.2A_UCC28070A_PFC.pdf

Regards,

Rajasekaran S

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

Please suggest what type/model of to be used for PFC choke to achieve >92% efficiency.

Details enclosed for reference.

WBDesign16_390Vdc@9.2A_UCC28070A_PFC.pdf

Regards,

Rajasekaran S

Hi Rajasekaran,

Could you help to clarify your question? Are you asking for a review of the schematic your shared or are you asking for topology recommendation to achieve 92% efficiency? What operating condition do you need to achieve 92% efficiency? What is the total output power and input voltage range?

Best Regards,

Ben Lough

Hi Ben,

1. Please confirm the schematic is OK or any thing to improve.

2. Input Voltage - 85-265Vac, 47-63Hz

3. Output Power - 390Vdc, 9.2A

4. What type of core and size to be used for PFC Choke

5. Consider efficiency should be >95% for entire input range

Thanks & Regards,

Rajasekaran S

Hi Rajasekaran,

1. The boost inductors seem quite small at 11.5uH each. For reference, this 5kW reference design uses 360uH. For a CCM PFC, the expectation is that the inductor current is CCM and only dropping into DCM near the AC zero crossing. I would suggest to double check this. It may also be worthwhile to use the reference design and adjust for your purposes here. The reference design has already been tested after all.

4. I would suggest to reach out to your magnetics vendor to discuss this topic.

5. 95% is going to be difficult at low line input. If you really need 95% across the entire input range, I would suggest taking a look at bridgeless PFC alternatives like AC switch or totem pole.

Best Regards,

Ben Lough

Hi Ben Lough,

Thanks for your support.

1. The value is arrived based on web designer only. Please suggest for approximate values. For 5KW reference design uses 360uH, in that Vin=180-264VAC only.

4. Ok. let me check with magnetics vendor.

5. OK. thanks.

6. Another query, whatever load from 0.5A to 9.2A, both mosfets will share load or any one mosfet will share for light load.

7. Which section to be checked for output voltage is dropped from 390v to 340v for 1A load.

Thanks & Regards,

Rajasekaran S

Hi Rajasekaran,

1. Ok, I will review again and suggest a value.

6. This controller does not have phase shedding. The FETs will share the load at light load

7. I would suggest to check if the max duty cycle clamp is limiting the on time at 1A load. Check VSENSE if the drop in output voltage is able to be seen by the controller. Check CSA and CSB to check if the cycle by cycle peak current limit is terminating the gate pulse early.

Best Regards,

Ben Lough

Hi Ben,

Thanks for your support.

1. Please suggest value for PFC Choke.

8. Kindly review the schematic and confirm any thing to be modified?. We have used Fsw-200KHz, its ok or not?

Thanks & Regards,

Rajasekaran S

Hi Rajasekaran,

1. I would suggest 200uH for the boost inductors. Could you fill out a UCC28070 design calculator? It will help to understand your preferences.

2. 200kHz is pretty fast. The switching losses at this power level may be a bit high. Any reason for wanting to switch this fast? Most designs will switch ~100kHz.

Best Regards,

Ben Lough

Hi Ben,

Thanks for your continuous support.

1. OK, i will try with 200uH using PQ4040 core. In ucc28070 design calculator, it shows less value like 23uH for 100Khz and 11.84uH for 200Khz.

2. OK, now i will go with 100Khz.

3. Whether we can use less than 100Khz also like 35 or 65Khz, any effect is there like regulation, efficiency, power factor.

4. We checked CSA & CSB signals are ok with values of 320mV.

5. When we loaded for 500w or any load phase B, PFC choke is getting heated and voltage drop is there in bridge output. Bridge diode 50A, 1000V are using.

Thanks & Regards,

Rajasekaran S

Hi Rajasekaran,

There are a few items to consider when selecting the switching frequency. For a CCM PFC, you want the inductor currents to be continuous conduction. If the frequency is too low, the inductor current becomes discontinuous and the power factor will suffer. Too low of a switching frequency will also mean higher peak currents in the boost power stage. Too high of a switching frequency will lead to excessive switching losses in the power stage. You will want to consider the reverse recovery of the boost diode for example. Many CCM PFC designs will use ultra fast or even silicon carbide diodes for the better switching performance. The switching performance of FETs you pick should also be considered here.

Could you expand on your last point? Both phase A and phase B should be sharing the same load since this is an interleaved PFC. Are the two phases being loaded differently? Any waveforms you could share to help illustrate the issue?

Best Regards,

Ben Lough

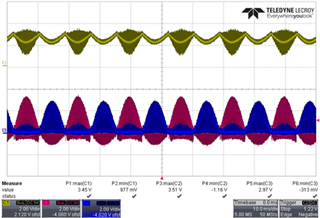

Hi Rajasekaran,

Apologies but I am not able to tell much from this waveform (I assume these are the gate drive signals?). Please share the following waveforms.

1.CSA

2.CSB

3.CAOA

4.CAOB

5.GDA

6.GDB

Best Regards,

Ben Lough

Hi Rajasekaran,

Apologies for the delay. These waveforms look like they are of light load operation where the UCC28070 is entering zero power detection in some cases. Could you share a waveform of CSA and CSB when your output starts to droop like you mentioned previously?

Best Regards,

Ben Lough

Hi Ben,

Thanks for your patience.

wave form enclosed for your reference.

Thanks & Regards,

Rajasekaran S

Hi Rajasekaran,

Apologies for the delay. Let me share with you what the CSA and CSB waveforms are supposed to look like. Ch1=Rsynth, Ch2=CSB, Ch3=CSA. The CSA and CSB signals are supposed to be resemble the inductor current for each phase.

From your waveform, it looks like at least in the time window shown in the scope capture the IC does not see the CSx signals hit the 3.3V peak current limit. So check the other signals in the feedback chain that might explain the droop.

1. What is the voltage of VAO when the output droops? If the output voltage is drooping then the expectation is the VAO signal will increase to compensate the drop in output voltage. Is it hitting the 5V limit for the pin?

2. Check CAOA and CAOB. These are the reference signals for the PWM comparators for each phase. Are the CAOA and CAOB voltages clos to the 6V ceiling or are they pulled low indicating the controller is detecting a fault?

3. Check the shape of the IMO signal. Does it resemble a rectified sinusoid at 2x the line frequency? Or is it distorted?

4. Check your duty cycle setting for DMAX. Is the controller running into the duty cycle limit at the heavier load?

Best Regards,

Ben Lough