Other Parts Discussed in Thread: EV2400

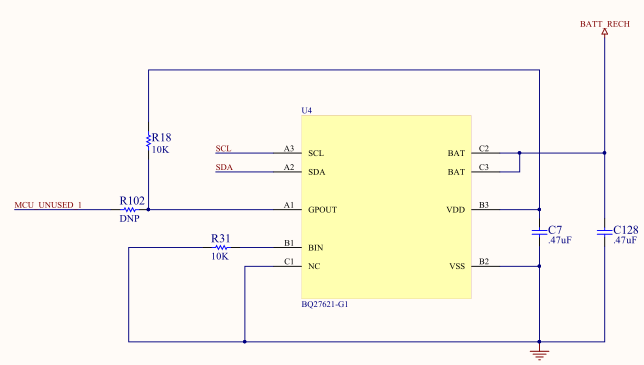

I am working on a bug for a customer where certain units fail to communicate via I2C with the BQ27621-G1 fuel gauge. The host processor is an STM32F4 part (sorry, TI ). Here is our circuit design:

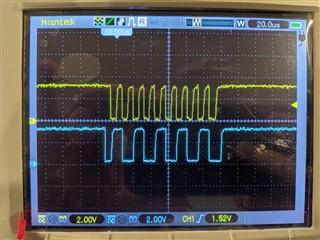

It has been quite difficult to characterize this mode. The few times I have been able to duplicate it in a controlled way is by disconnecting the battery, waiting until any voltage in the circuit dissipates (particularly across VBAT), then reconnecting the battery. Once the part is in this state, it NACKs any I2C communication until a power cycle, like so:

I measured what I could around the circuit while the chip is in this state:

- VDD = 1.81V

- VBAT = 3.93V

- GPOUT = 1.79V

- BIN = 0.00V

- SCL & SDA idle = 3.01V (pulled up to 3.3V elsewhere in our schematic)

- The I2C peripheral is operating properly, as communication with other slaves continues.

Things I have tried to get out of this mode:

- Slow down I2C clock from 100khz down to 10khz

- Toggle GPOUT low & release (manually with a probe)

- Toggle BIN low & release (manually with a probe)

- Hold both SDA and SCL lines LOW for 2 sec (in firmware)

- Send a RESET Control() command

I have seen several other forum posts with this issue, but they either have suggested what I have already tried above, or there was no resolution. Please help!