Hello,

We have created a design withe the BQ25570 charging 2 supercaps of 5F.

The photovoltaics cells are monocrystallin ref SM141K06LV.

Parameters are:

VBAT_OV = 5V

VBAT_OK = 2,2V

VBAT_OK_HYST = 2,8V

VOUT = 2V

We have 2 problems:

- when we connect cells first time teh BQ never starts and there is only 0,1V on the cells with a good sun. Cells semmes to be shorted. (Open circuit voltage on cells is about 3V)

=> To start we must put a voltage on VIN, the BQ becomes hot during a few second and after the boost reg starts normally. Volatge on cells at this time is about 2,5V)

The voltage on VBAT reach about 3,3V

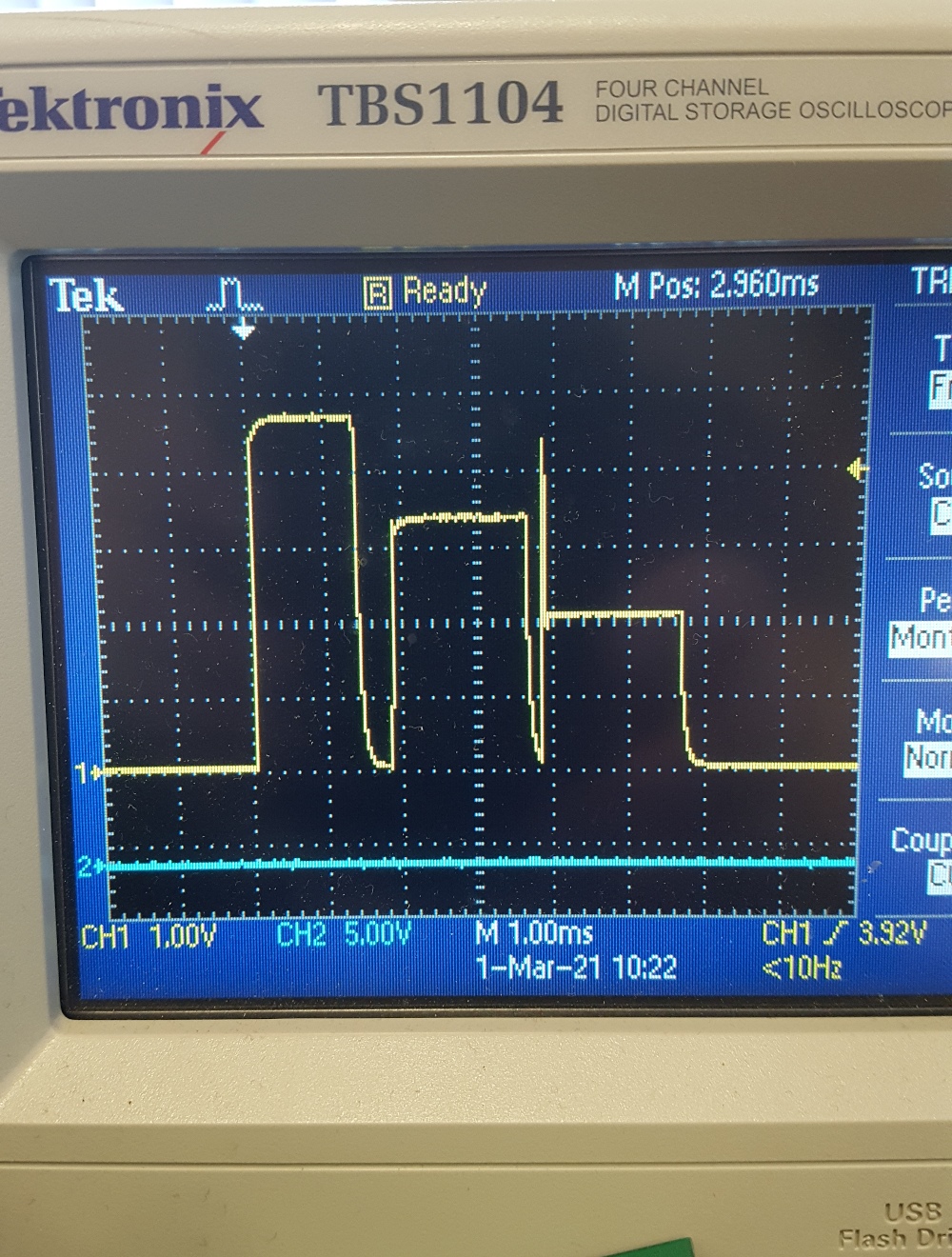

- The second problem is that the VBAT_OK never goes high so the buck reg never start.

Please could you help us to make this design working well ?

Thank you by Avance

If you want we can send you our schematic.

Regards

Thierry