Engineering desires to use the TPS546D24A AVIN/PVIN common input voltage, 3.3V, as the pullup source for the PGD pin.

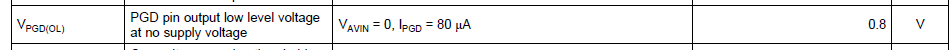

Am I correct to assume that if I follow the IPGD test condition that the Power Good specification , 0.8V shown below, will be maintained until the POR completes.

Spec indicates PVIN is already at 12V and AVIN at 0V, just trying to verify that there will not be any spurious indications of PG while device is powering up.

This would equate to an ~33.3K ohm resistor from 3.465V (max input rail voltage) to limit current to 80uA if the PGD pin is 0.8V.

(3.465V-0.8V)/80uA = ~33.3K ohm

Thanks,

Brad