Other Parts Discussed in Thread: TPS3828

Hi,

I came across a powerup issue with TPS3128E18.

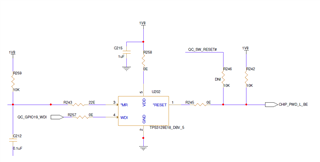

Schematic:

- MR#: connected to pushbutton (to assert manual HW_RESET). Currently not used, constant pullup.

- WDI: Watchdog input from the processor.

- RESET#: connected to the processor HW_RESET input.

1V8 is clean and stable.

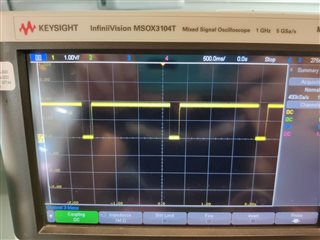

My problem is occurring on new boards arriving from manufacturing line, where WDI is at high-impedance (processor not flashed) and yet RESET# still assert reset patterns (see scope shot).

In order to verify WDI is indeed high impedance, R257 (from WDI input) was removed - component's WDI is open - and reset pattern persists.

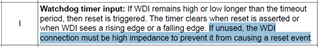

The data sheet stated that such reset event should have been avoided.

Please advise.

Thanks,

Amit