Other Parts Discussed in Thread: TPS54360, LMR36006, LMR36015

Hi TI,

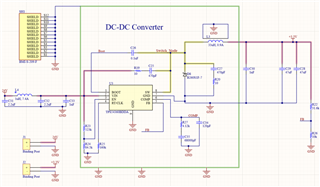

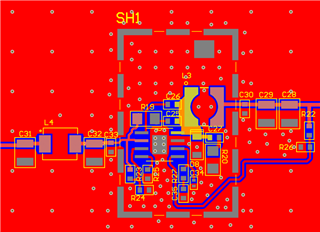

I am developing a DCDC supply for an academic project related to EMC. The design I have built on PCBs converts 24V to 3.3V and delivers 500mA. We are trying to pass CISPR 25 Class 5 emissions requirements, but every time we make changes that would traditionally work we are seeing significantly more noise and an increase in ringing. Originally we were running the supply at 680kHz, but we increased that to about 800kHz and we are seeing cleaning switching, but it is still not reacting to the EMC countermeasures the way we would expect.

I was hoping to speak to an AE that is familiar with this IC to get their input on the design.

Thank You

Nick