Hello,

We are facing problem while using BQ76952 to turn OFF MOSFETs during a short circuit event during discharge. The MOSFETs were initially ON at no load and suddenly a short circuit was created.

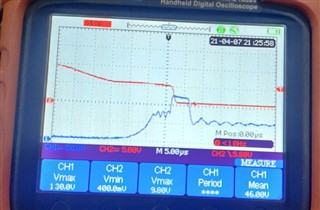

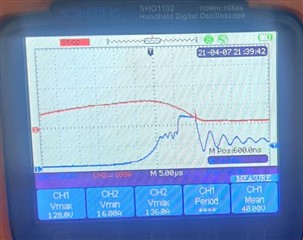

The schematic of the system is attached. We are using a Cgd value of 100pF on each of the 4 MOSFETs to remove oscillation faced at low loads during turn OFF. Please see the waveform of current during short-circuit and Vgs of Discharge FET. Only the discharge FET is failing, and nothing happens to charge FETs. Also, the SCD limit was 20A but the current went as high as 130A. Is this a response time issue? Please suggest how to correct the situation.