Hello,

I am using the TPS56C215 buck regulator and after simulation, I am facing a bug in the model.

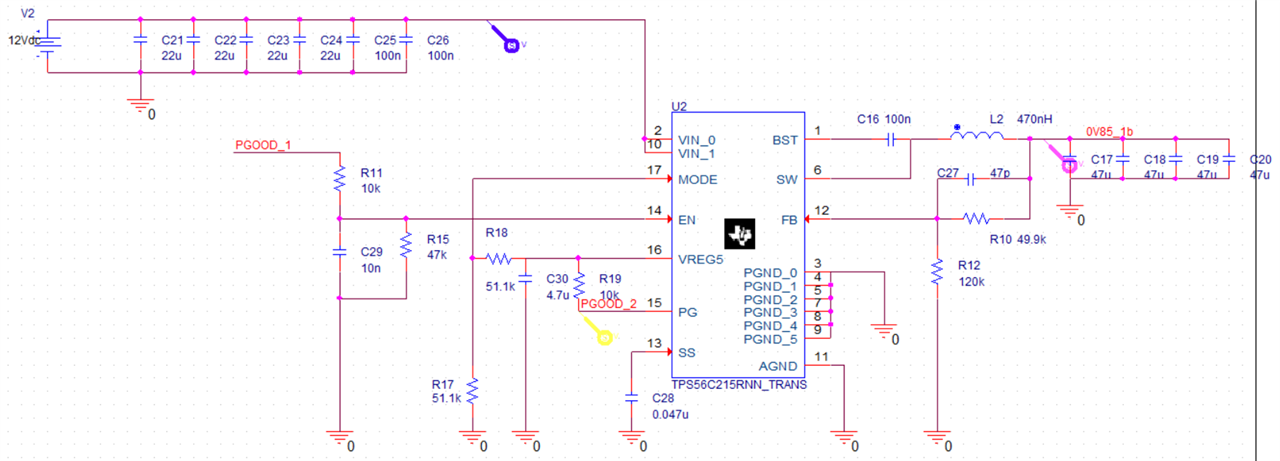

The schematic :

The simulation :

The problem is that P_GOOD2 (yellow) pin is "HIGH" when the output (pink) start rising.

I think there is a mistake in the model or something wrong in my simulation.

Thanks for help me