Other Parts Discussed in Thread: UCC27714EVM-551,

Hello,

This thread is a continuation of the following one, as recommended: UCC27714EVM-551: how to test cycle-by-cycle current limit - Power management forum - Power management - TI E2E support forums

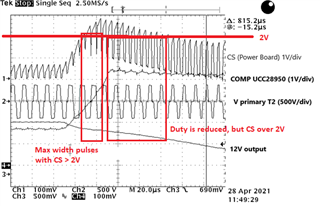

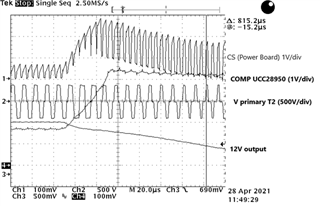

I applied a short circuit at the output of the UCC27714EVM-551, and finally I got a level over 2V in the CS signal.

During the first pulses, while the COMP pin is increasing its level up to saturation, there's no cycle-by-cycle current limit, and full-width pulses are applied to the transformer, despite CS being well above 2V. Approximately when the COMP pin saturates, then the pulse-width starts to decrease.

Why there's no cycle-by-cycle current limitation at the start of the short-circuit? Does this mode depend on the COMP in addition to the CS level?

-------------------------------------------------------------------------------------------------------------------

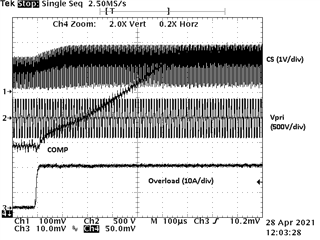

This behaviour seems to be different with an overload (from 50A to 65A approximately) instead of a short-circuit.

Here it can be seen that even applying a step-load (passive and non-inductive), the primary current is increasing slowly, so there's a current limitation with the COMP not saturated.

Who is limiting the primary current in the first pulses when the step-load is applied?

This mechanism is limiting the peak current with an overload but not with a short circuit. So the cycle-by-cycle current limit seems to be more complicated than a comparator than compares the (CS+RAMP) with 2V.