Other Parts Discussed in Thread: UCC3818, UC3854

Hi all,

We are using the UCC2818 with the synchronisation circuit refered in application note "SLUA245 - July 2000".

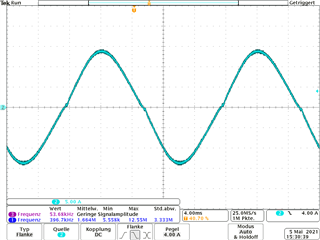

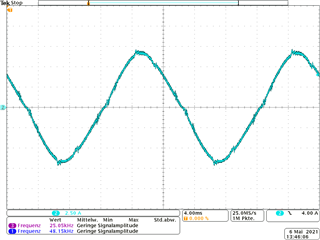

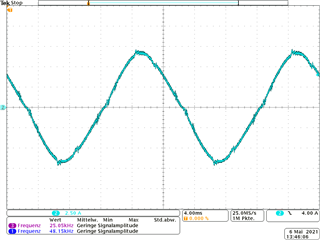

Like described in application note "SLUA296A - October 2003 -- Revised April 2010" we can observe the negative effects on the current (left image).

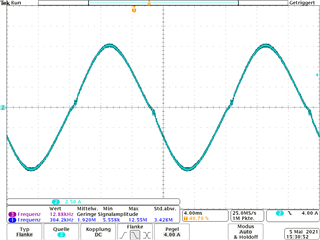

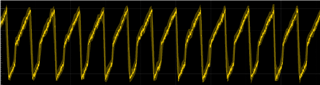

Without synchronisation (and a smaller CT to maintain 145kHz switching frequency) those effects are non present anymore (right image).

However in free running mode the frequency tolerance from the datasheet is very high with +/-20%.

Which parameters have the most effect on this variation?

Assuming RT and CT have 0% tolerance what would be:

-the variation between different devices?

-the drift from the initial frequency over a lifetime of 10 years?

Best regards,

Michael