Hi,

We are using TPS63010YFFR in our enterpise mobile phone design. We are observing an issue with respect to leakage current in TPS63010 in some of the boards.

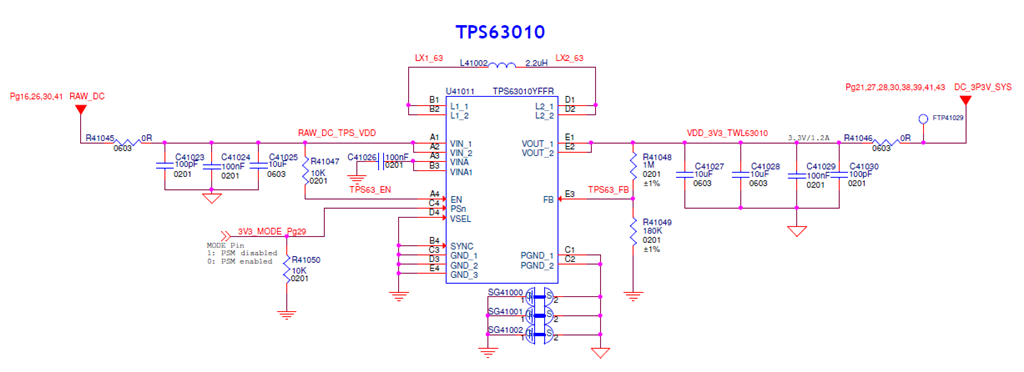

The TPS schematics in our design is as below:

- Input to TPS is 4V(RAW_DC)

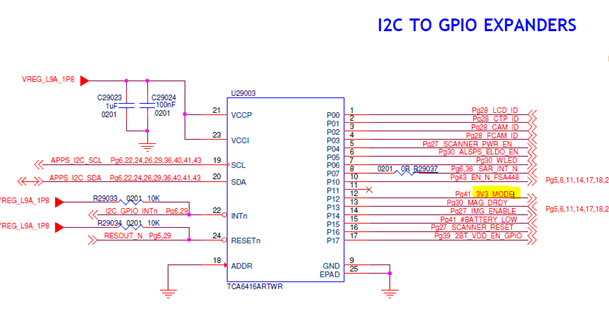

- PSn pin(3V3_Mode) is driven by an I2C based GPIO expander

The setup to measure leakage current is as below:

- An input of 4V is fed to the board without powering ON the board.

- A leakage current of around 6mA is observed in some of the boards, roughly in 4 out of 15 boards that we have.

- If the TPS63010 is disabled by pulling the enable pin low, leakage current is not observed thus proving that the leakage is indeed caused by TPS63010.

- This leakage current is observed when the board is first powered up.

- If the power supply is removed and fed back immediately, the leakage current is not observed.

- If the power supply is removed and fed back once the output capacitor is completely discharged(takes around 10-15 seconds), the leakage current is again observed.

- The output voltage in both high and normal leakage current cases is about 3.25V.

We have captured the waveforms(LX1, LX2, VOUT ripple) with and without the leakage current. Please find the doc with images attached.

We tried the following experiments:

- Isolated the PSn pin from the GPIO Expander and pulled it down to ground through 0 Ohm(R41050), the leakage current(~6.2mA) was still observed.

- Isolated the load connected to TPS63010 by removing output series resistor (R41046), the leakage current still remained.

- We swapped the TPS63010 chip between a good and a bad board and the issue followed the IC, i.e, Good board started showing leakage current and the bad board was normal. We performed this experiment twice with different set of boards and the observations were same.

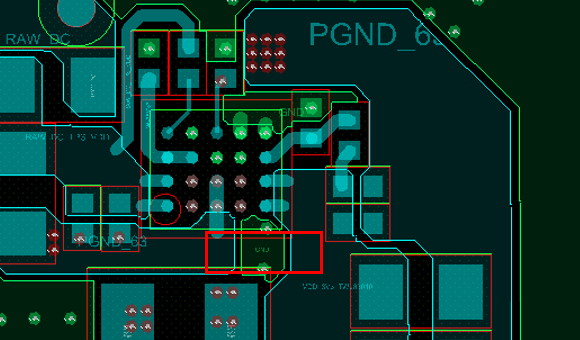

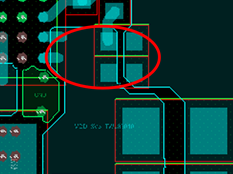

The layout section of the TPS63010 is attached for your review.

Since this issue is not reproducable in all the boards, we are finding it hard to figure out the root cause for this leakage current.

Kindly review the design and our observations. Please do let us know if you need any inputs from us.

Your timely suggestions and inputs would be invaluable for us as we are approaching the Mass production stage for this product.

Thanks,

Naveen