Hi Team,

Customer is using BQ76952 and did a 12S BAT pack prototype, but during the short-circuit testing they found a issue that:

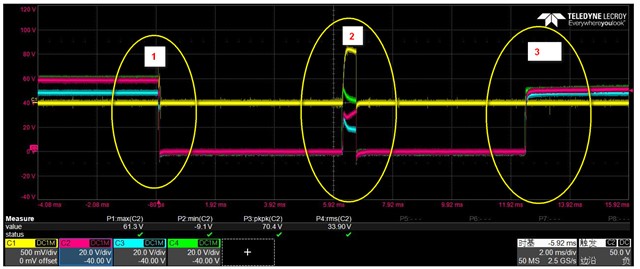

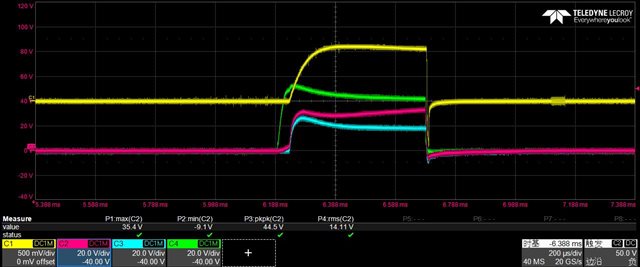

- At short circuit status, BQ76952 DSG voltage will change to ‘High’ automatically ~every 6ms, which may cause the MOSFET be broken.

- If short circuit protection be trigged, BQ76952 will change from ‘SEAL mode’ to be ‘UNSEL mode’ itself.

- Enclose please also refer to the gg file and log information (bqz firmware version is 0.36).

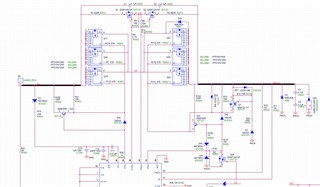

Attached is related part's schematic, log date & gg file, also the testing waveform as below, could your kindly check it and suggest what’s the potential reason & further experiment to verify the root cause?

|

|

|

CH1: of DSG_FET CH2: of DSG_FET of DSG_FET of BQ76952 |

CH1: of DSG_FET CH2: of DSG_FET of DSG_FET of BQ76952 |