Other Parts Discussed in Thread: USB2ANY, TPS650860EVM-116, IPG-UI, CSD87381P

Hi

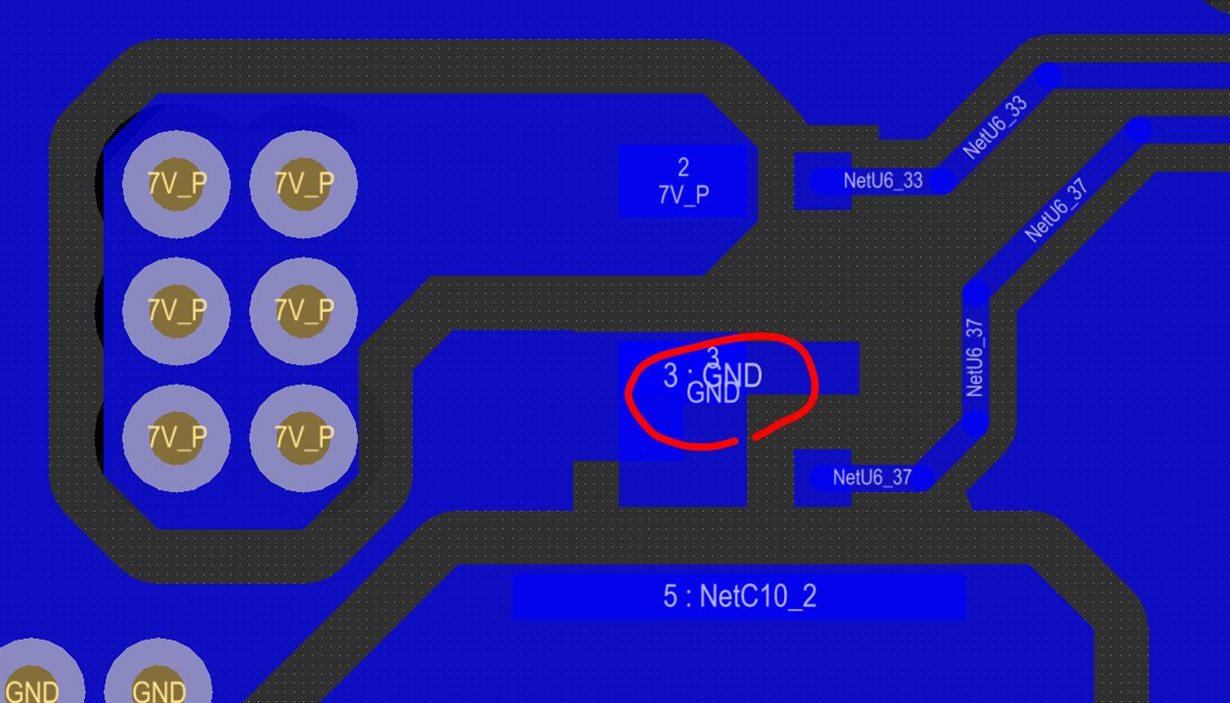

I designed the TPS6508641 for ZU4EG.

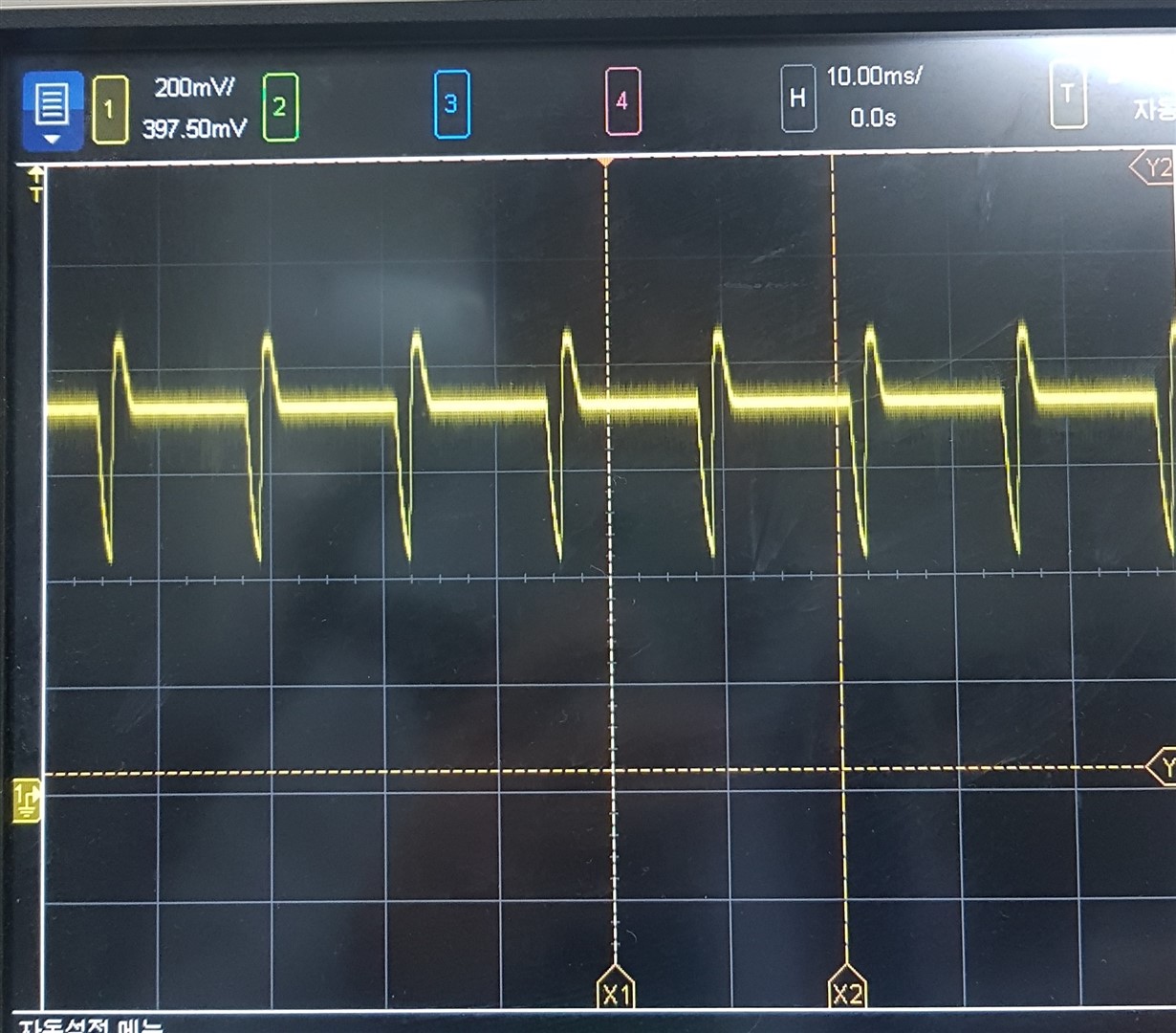

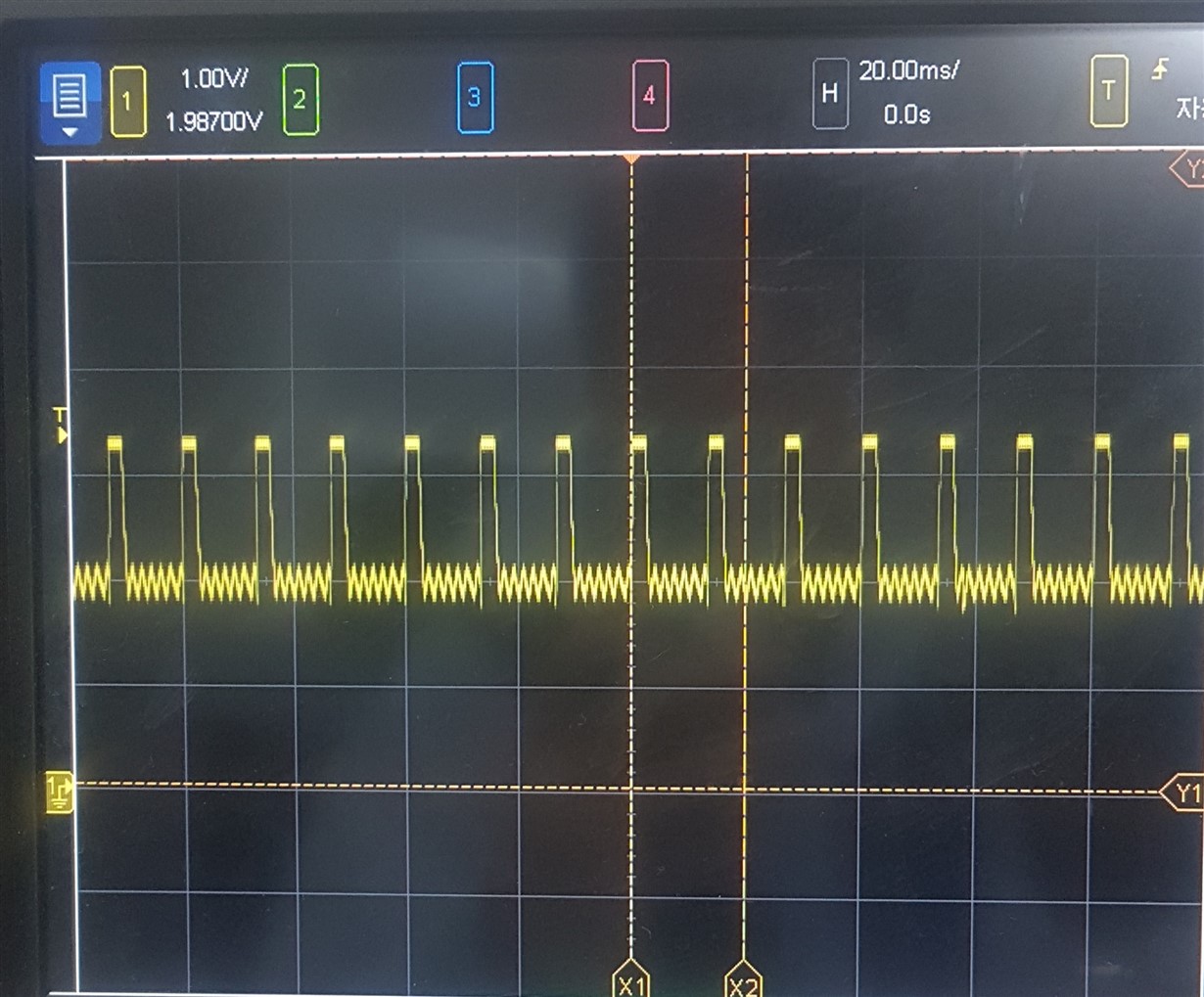

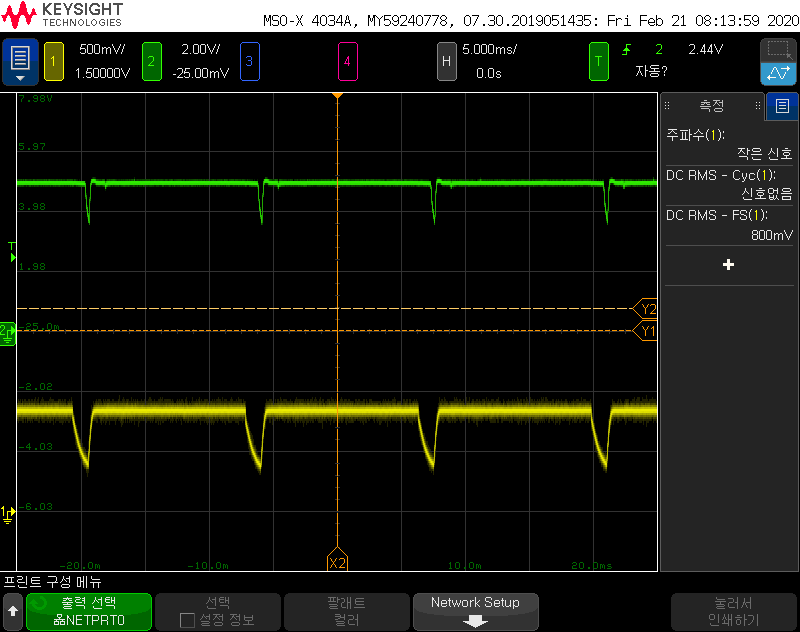

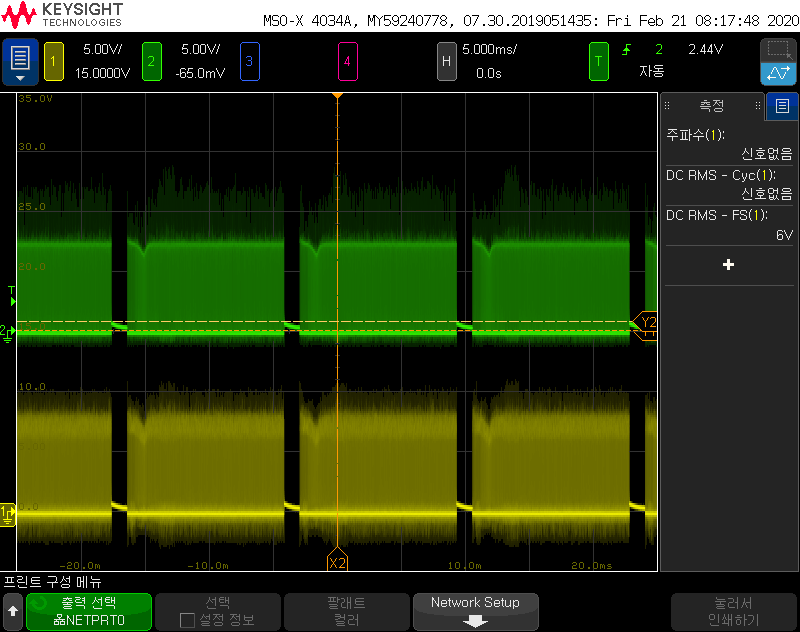

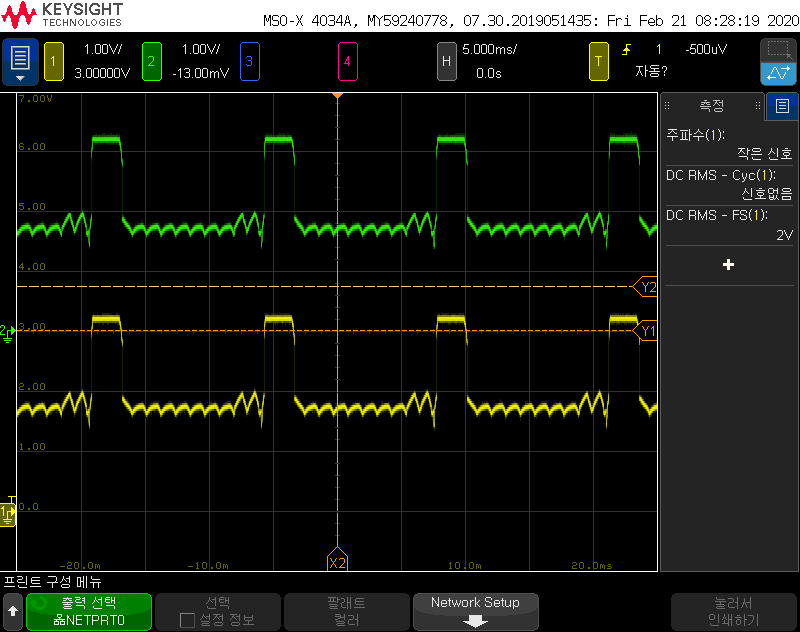

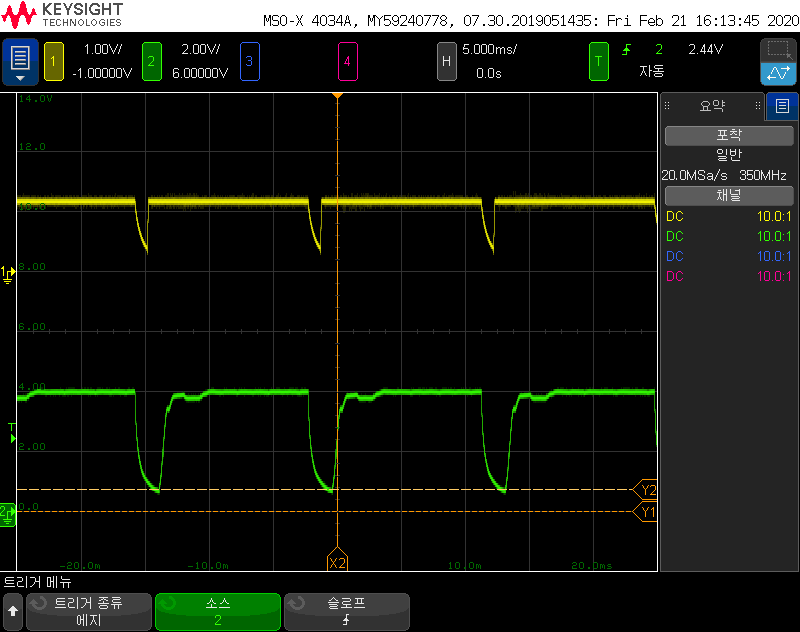

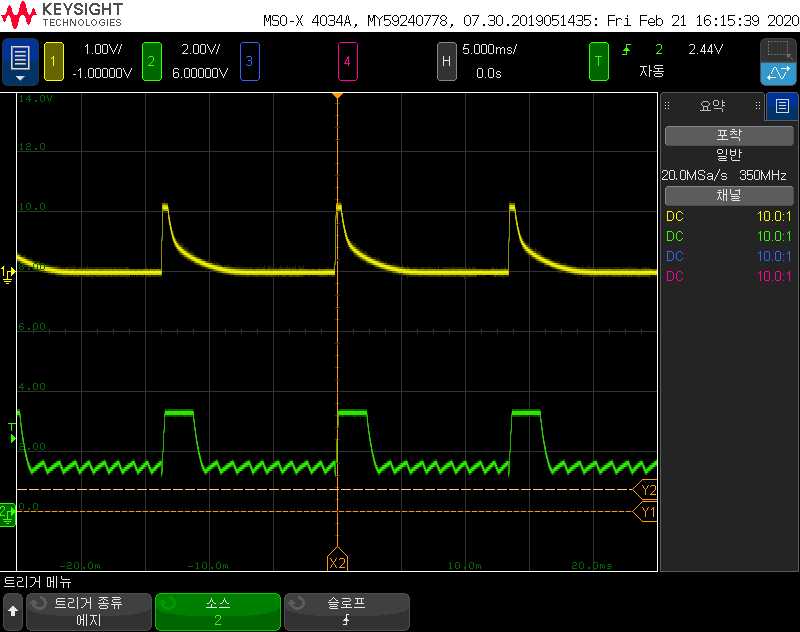

When I power up, buck2(0.85V) drop as shown below.

I attached my schematic.

One thing the sure, buck1 output is normal.

but when Buck2 output occur, Buck1 also dropped like the above picture.