Other Parts Discussed in Thread: LP5907, ADS1298, , TPS7A02, TPS723, TPS62243, LM27762, LM2664

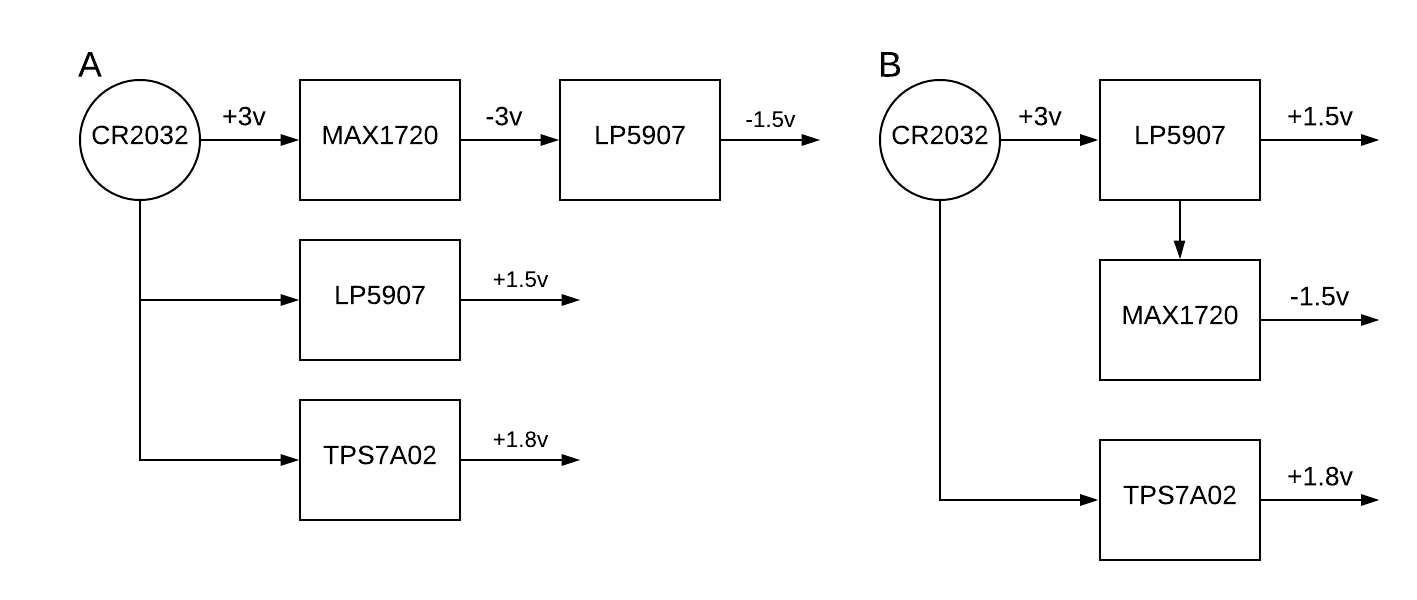

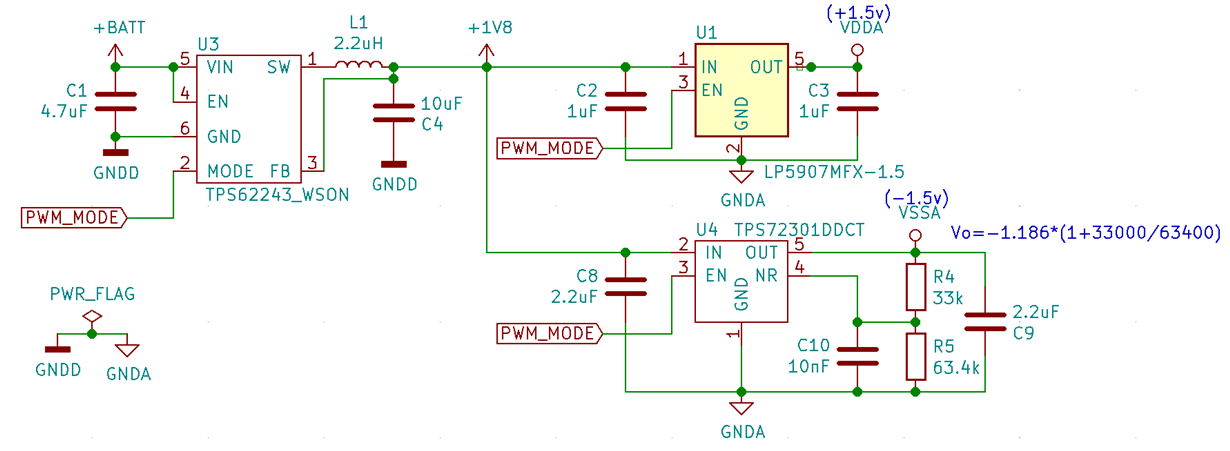

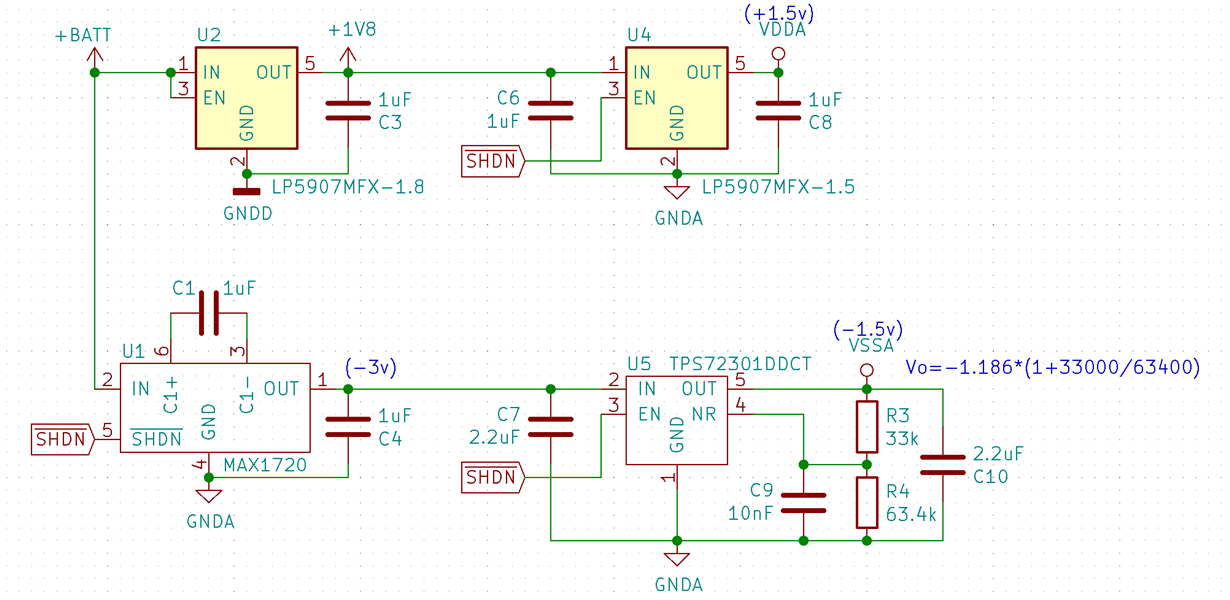

I'm considering using a 3v coin cell to power 1.8v components (micro, accelerometer, ADC; 20mA total) but also need a +/-1.5v for the ADC (specifically, ADS1298 to measure ECoG). Low Iq and noise are needed for the 1.5v supply, as it will often be shutdown/disabled. I see one option in the LP5907 for 1.5v:

LP5907 – Low-Iq (12uA); low noise (6.5uVrms); Low dropout (~120mV) (TPS7A20 is slightly better, but not available right now)

For the 1.8v regulation, there are a number of options since noise is not as critical. Low Iq may or may not be an issue, but the TPS7A02 seems to fit the bill:

TPS7A02 – Ultra-low Iq (25nA, 3nA shutdown); higher noise (130uVrms); higher dropout voltage (~400mV)

However, the LP5907 seems to offer better noise and dropout performance at the expense of higher Iq—in the case where Iq isn't a concern, should I just use the LP5907 for both regulators?

Lastly, to generate -1.5v I have used a voltage inverter in the past (MAX1720)—is this the best method/solution? Are there advantages to using a negative-output LDO?

*Note: the ADS1298 dev board where 5v is first inverted to -5v (using TPS6040x) and then makes +2.5 and -2.5 with independent TPS73201 chips (plus a +3v line with TPS73230). Is this design (A) preferred over directly inverting the ADC negative voltage ((B) e.g., +1.8v inverted to -1.8v, design)? The high Iq of the TPS73201 at 0.4mA makes it a poor option for me.