Other Parts Discussed in Thread: AM6442, , AM62P, SYSCONFIG

Tool/software:

Hi TI Experts,

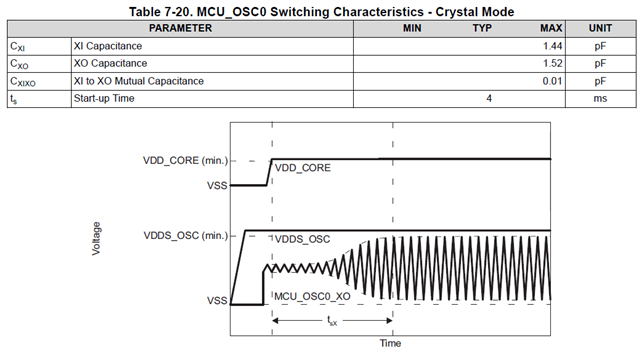

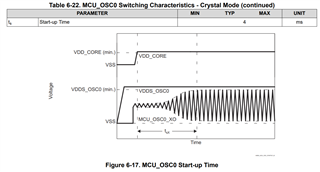

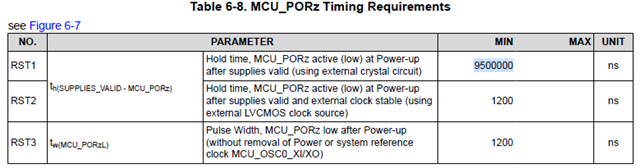

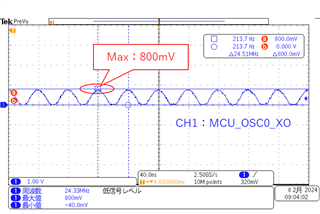

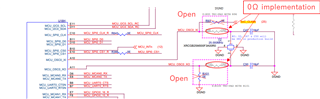

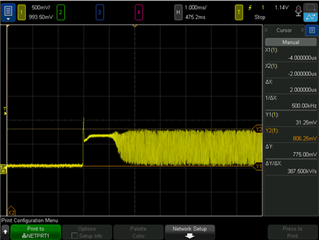

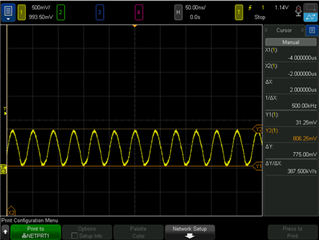

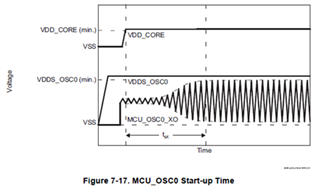

I have a question about "Figure 7-16. MCU_OSC0 Start-up Time" from the datasheet. Here it looks like that MCU_OSC0 is only allowed to start when VDD_CORE is ramping. In reality the oscillation starts already with VDDS_OSC0, while VDD_CORE is still disabled.

I assume that this is OK and not causing any problems?! But if this is the case, why is the Start-up Time ts shown relative to VDD_CORE stable? Shouldn't it be related to VDDS_OSC0 stable?