Other Parts Discussed in Thread: AM4377, SYSBIOS

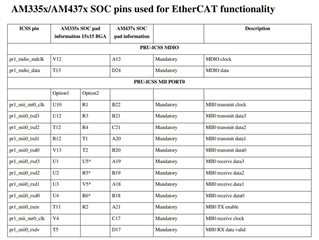

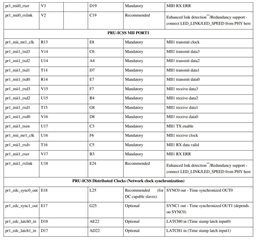

We are using the AM4377 processor as an EtherCAT slave device. In the past TI have provided a firmware API guide which states that specific pins must be used for the SOC pins used for EtherCAT ie the pin muxing does not work in the way that it does for the remainder of the host processor I/O. See the pictures below:

In the recent documentation I can find no reference to these specific pins being required for EtherCAT. Does this mean that this is no longer required and the SOC pins can be selected using the pin muxing scheme ie different pins can be used for EtherCAT according to the Pin Mux Tool?

Regards, Garry