Part Number: PROCESSOR-SDK-J784S4

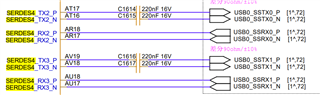

question:Unable to recognize device after entering fastboot mode.However, if the configuration is changed to the original development board and set to serdes0, the device can recognize it normally

May I ask if there are any errors regarding the configuration of serdes?

The schematic diagram of our USB and SERDES is shown in the following figure.

Connect USB 0 to LAN2 and LAN3 of serdes4.

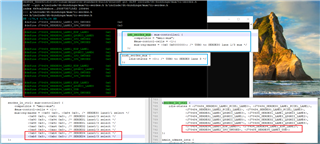

设备树配置如下: