Dear TI expert,

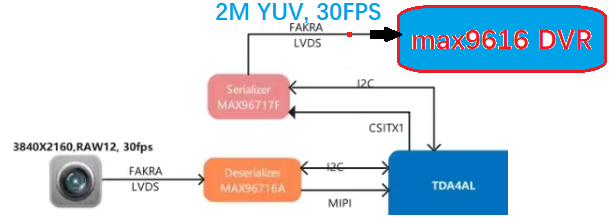

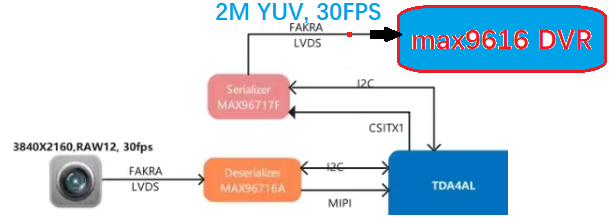

Our front camera is 8M. We need to output 8M YUV to the algorithm, and then need to crop the 8M YUV to 2M and output it to DVR through a deserializer. How to crop 8M YUV to 2M , and How to put 2M yuv to CSITX1? Thanks.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Dear TI expert,

Our front camera is 8M. We need to output 8M YUV to the algorithm, and then need to crop the 8M YUV to 2M and output it to DVR through a deserializer. How to crop 8M YUV to 2M , and How to put 2M yuv to CSITX1? Thanks.

Hi Qin,

Sure, lets see now why dss initialization is not working.

Since you don't have CCS + JTAG, we will have to put the prints at multiple places to try to see why part is not working.

I see it is stuck after below statement in the log.

[MCU2_0] 15.691574 s: DSS: SoC init ... Done !!!

First can you please set the display to some invalid value, so that it does not go and configure some of the board modules, in the file ti-processor-sdk-rtos-j721e-evm-08_06_00_12\vision_apps\platform\j721e\rtos\common\app_init.c, like below.

prm.display_type = 0x100;

status = appDssDefaultInit(&prm);

APP_ASSERT_SUCCESS(status);

Can you try with the above change and see if dss initialization completes? If not, lets again get the log and see where it hangs?

Regards,

Brijesh

[MCU1_0] 0.025397 s: CIO: Init ... Done !!!

[MCU1_0] 0.025479 s: ### CPU Frequency = 1000000000 Hz

[MCU1_0] 0.025530 s: CPU is running FreeRTOS

[MCU1_0] 0.025559 s: APP: Init ... !!!

[MCU1_0] 0.025586 s: MEM: Init ... !!!

[MCU1_0] 0.025630 s: MEM: Created heap (DDR_LOCAL_MEM, id=0, flags=0x00000004) @ d8000000 of size 8388608 bytes !!!

[MCU1_0] 0.025726 s: MEM: Init ... Done !!!

[MCU1_0] 0.025757 s: IPC: Init ... !!!

[MCU1_0] 0.025820 s: IPC: 6 CPUs participating in IPC !!!

[MCU1_0] 0.025873 s: IPC: Waiting for HLOS to be ready ... !!!

[MCU1_0] 11.943780 s: IPC: HLOS is ready !!!

[MCU1_0] 11.965111 s: IPC: Init ... Done !!!

[MCU1_0] 11.965183 s: APP: Syncing with 5 CPUs ... !!!

[MCU1_0] 12.414920 s: APP: Syncing with 5 CPUs ... Done !!!

[MCU1_0] 12.415204 s: REMOTE_SERVICE: Init ... !!!

[MCU1_0] 12.422229 s: REMOTE_SERVICE: Init ... Done !!!

[MCU1_0] 12.422304 s: APP: Init ... Done !!!

[MCU1_0] 12.422339 s: APP: Run ... !!!

[MCU1_0] 12.422368 s: IPC: Starting echo test ...

[MCU1_0] 12.426585 s: IPC: Echo status: mpu1_0[x] mcu1_0[s] mcu2_0[x] mcu2_1[x] C7X_1[P] C7X_2[x]

[MCU1_0] 12.427196 s: APP: Run ... Done !!!

[MCU1_0] 12.427344 s: IPC: Echo status: mpu1_0[x] mcu1_0[s] mcu2_0[x] mcu2_1[x] C7X_1[P] C7X_2[P]

[MCU1_0] 12.428580 s: IPC: Echo status: mpu1_0[x] mcu1_0[s] mcu2_0[x] mcu2_1[P] C7X_1[P] C7X_2[P]

[MCU1_0] 12.429957 s: [MCU1_0] IPC regist cb status = 0

[MCU1_0] 12.430503 s: can_func_Task create !!!

[MCU1_0] 12.430554 s: can_func_Task RUN !!!

[MCU1_0] 12.430586 s: -----CAN--Func TASK run-------

[MCU1_0] 12.450710 s: CrossBar/Interrupt Configuration done.

[MCU1_0] 12.450775 s: MCANSS Revision ID:

[MCU1_0] 12.450804 s: scheme:0x1

[MCU1_0] 12.450833 s: Business Unit:0x2

[MCU1_0] 12.450865 s: Module ID:0x8e0

[MCU1_0] 12.450895 s: RTL Revision:0xa

[MCU1_0] 12.450925 s: Major Revision:0x1

[MCU1_0] 12.450955 s: Custom Revision:0x0

[MCU1_0] 12.450987 s: Minor Revision:0x1

[MCU1_0] 12.451019 s: CAN-FD operation is enabled through E-Fuse.

[MCU1_0] 12.451057 s: Endianess Value: 0x87654321

[MCU1_0] 12.451387 s: CrossBar/Interrupt Configuration done.

[MCU1_0] 12.451432 s: MCANSS Revision ID:

[MCU1_0] 12.451462 s: scheme:0x1

[MCU1_0] 12.451490 s: Business Unit:0x2

[MCU1_0] 12.451520 s: Module ID:0x8e0

[MCU1_0] 12.451549 s: RTL Revision:0xa

[MCU1_0] 12.451580 s: Major Revision:0x1

[MCU1_0] 12.451610 s: Custom Revision:0x0

[MCU1_0] 12.451642 s: Minor Revision:0x1

[MCU1_0] 12.451673 s: CAN-FD operation is enabled through E-Fuse.

[MCU1_0] 12.451720 s: Endianess Value: 0x87654321

[MCU1_0] 12.452281 s: ADC : ADC application started...

[MCU1_0] 12.452344 s: ADC application started...

[MCU1_0] 12.452377 s: ADC : ADC App_Udma_init !!

[MCU1_0] 12.452413 s: ADC App_Udma_init !!

[MCU1_0] 12.453004 s: ADC : ADC App_adcInit started...

[MCU1_0] 12.453083 s: ADC App_adcInit started...

[MCU1_0] 12.453696 s: ADC : ADC App_adcInit end!!!.

[MCU1_0] 12.453737 s: ADC App_adcInit end!!!.

[MCU1_0] 12.453766 s: ADC : ADC App_adcInit started...

[MCU1_0] 12.453803 s: ADC App_adcInit started...

[MCU1_0] 12.454683 s: ADC : ADC App_adcInit end!!!.

[MCU1_0] 12.454719 s: ADC App_adcInit end!!!.

[MCU1_0] 12.454747 s: ADC : ADC App_create started...

[MCU1_0] 12.454783 s: ADC App_create started...

[MCU1_0] 12.455200 s: ADC : ADC App_create Udma_chOpen gADC_0_RX_PDMA_CH end...

[MCU1_0] 12.455274 s: ADC App_create Udma_chOpen gADC_0_RX_PDMA_CH end...

[MCU1_0] 12.455593 s: ADC : ADC App_create Udma_chOpen gADC_1_RX_PDMA_CH end...

[MCU1_0] 12.455654 s: ADC App_create Udma_chOpen gADC_1_RX_PDMA_CH end...

[MCU1_0] 12.456169 s: ADC : ADC App_create end !!!!...

[MCU1_0] 12.456243 s: ADC App_create end !!!!...

[MCU2_0] 4.009312 s: CIO: Init ... Done !!!

[MCU2_0] 4.009362 s: ### CPU Frequency = 1000000000 Hz

[MCU2_0] 4.009392 s: CPU is running FreeRTOS

[MCU2_0] 4.009413 s: APP: Init ... !!!

[MCU2_0] 4.009432 s: SCICLIENT: Init ... !!!

[MCU2_0] 4.009562 s: SCICLIENT: DMSC FW version [8.6.3--v08.06.03 (Chill Capybar]

[MCU2_0] 4.009595 s: SCICLIENT: DMSC FW revision 0x8

[MCU2_0] 4.009622 s: SCICLIENT: DMSC FW ABI revision 3.1

[MCU2_0] 4.009652 s: SCICLIENT: Init ... Done !!!

[MCU2_0] 4.009675 s: UDMA: Init ... !!!

[MCU2_0] 4.010537 s: UDMA: Init ... Done !!!

[MCU2_0] 4.010572 s: UDMA: Init ... !!!

[MCU2_0] 4.011051 s: UDMA: Init for CSITX/CSIRX ... Done !!!

[MCU2_0] 4.011098 s: MEM: Init ... !!!

[MCU2_0] 4.011132 s: MEM: Created heap (DDR_LOCAL_MEM, id=0, flags=0x00000004) @ d9000000 of size 16777216 bytes !!!

[MCU2_0] 4.011188 s: MEM: Created heap (L3_MEM, id=1, flags=0x00000000) @ 60000000 of size 524288 bytes !!!

[MCU2_0] 4.011238 s: MEM: Init ... Done !!!

[MCU2_0] 4.011259 s: IPC: Init ... !!!

[MCU2_0] 4.011307 s: IPC: 6 CPUs participating in IPC !!!

[MCU2_0] 4.011341 s: IPC: Waiting for HLOS to be ready ... !!!

[MCU2_0] 12.249195 s: IPC: HLOS is ready !!!

[MCU2_0] 12.260869 s: IPC: Init ... Done !!!

[MCU2_0] 12.260919 s: APP: Syncing with 5 CPUs ... !!!

[MCU2_0] 12.414915 s: APP: Syncing with 5 CPUs ... Done !!!

[MCU2_0] 12.414949 s: REMOTE_SERVICE: Init ... !!!

[MCU2_0] 12.416368 s: REMOTE_SERVICE: Init ... Done !!!

[MCU2_0] 12.416410 s: FVID2: Init ... !!!

[MCU2_0] 12.416467 s: FVID2: Init ... Done !!!

[MCU2_0] 12.416492 s: SCICLIENT: Sciclient_pmSetModuleState module=219 state=2

[MCU2_0] 12.416731 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 12.417753 s: appGpioInit Done!!!

[MCU2_0] 12.417785 s: DSS: Init ... !!!

[MCU2_0] 12.417807 s: DSS: M2M Path is enabled !!!

[MCU2_0] 12.417829 s: DSS: SoC init ... !!!

[MCU2_0] 12.417850 s: SCICLIENT: Sciclient_pmSetModuleState module=158 state=0

[MCU2_0] 12.417945 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 12.417974 s: DSS: SoC init ... Done !!!

[MCU2_0] 12.418014 s: src/drv/common/dss_init.c @ Line 102:

[MCU2_0] 12.418040 s: qindh 1........

[MCU2_0] 12.418212 s: src/drv/common/dss_init.c @ Line 124:

[MCU2_0] 12.418239 s: qindh 2........

[MCU2_0] 12.418830 s: soc/V2/dss_soc.c @ Line 354:

[MCU2_0] 12.418857 s: qindh 1 Dss_enableL1Event........

[MCU2_0] 12.418887 s: soc/V2/dss_soc.c @ Line 358:

[MCU2_0] 12.418917 s: qindh 1.0 Dss_enableL1Event........

[MCU2_1] 4.006885 s: CIO: Init ... Done !!!

[MCU2_1] 4.006936 s: ### CPU Frequency = 1000000000 Hz

[MCU2_1] 4.006967 s: CPU is running FreeRTOS

[MCU2_1] 4.006988 s: APP: Init ... !!!

[MCU2_1] 4.007008 s: SCICLIENT: Init ... !!!

[MCU2_1] 4.007131 s: SCICLIENT: DMSC FW version [8.6.3--v08.06.03 (Chill Capybar]

[MCU2_1] 4.007164 s: SCICLIENT: DMSC FW revision 0x8

[MCU2_1] 4.007192 s: SCICLIENT: DMSC FW ABI revision 3.1

[MCU2_1] 4.007224 s: SCICLIENT: Init ... Done !!!

[MCU2_1] 4.007247 s: UDMA: Init ... !!!

[MCU2_1] 4.008267 s: UDMA: Init ... Done !!!

[MCU2_1] 4.008315 s: MEM: Init ... !!!

[MCU2_1] 4.008351 s: MEM: Created heap (DDR_LOCAL_MEM, id=0, flags=0x00000004) @ da000000 of size 16777216 bytes !!!

[MCU2_1] 4.008410 s: MEM: Created heap (L3_MEM, id=1, flags=0x00000001) @ 60080000 of size 524288 bytes !!!

[MCU2_1] 4.008463 s: MEM: Init ... Done !!!

[MCU2_1] 4.008485 s: IPC: Init ... !!!

[MCU2_1] 4.008540 s: IPC: 6 CPUs participating in IPC !!!

[MCU2_1] 4.008575 s: IPC: Waiting for HLOS to be ready ... !!!

[MCU2_1] 12.403086 s: IPC: HLOS is ready !!!

[MCU2_1] 12.414836 s: IPC: Init ... Done !!!

[MCU2_1] 12.414877 s: APP: Syncing with 5 CPUs ... !!!

[MCU2_1] 12.414915 s: APP: Syncing with 5 CPUs ... Done !!!

[MCU2_1] 12.414945 s: REMOTE_SERVICE: Init ... !!!

[MCU2_1] 12.416541 s: REMOTE_SERVICE: Init ... Done !!!

[MCU2_1] 12.416581 s: FVID2: Init ... !!!

[MCU2_1] 12.416680 s: FVID2: Init ... Done !!!

[MCU2_1] 12.416706 s: VHWA: DMPAC: Init ... !!!

[MCU2_1] 12.416729 s: SCICLIENT: Sciclient_pmSetModuleState module=58 state=2

[MCU2_1] 12.416911 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_1] 12.416939 s: SCICLIENT: Sciclient_pmSetModuleState module=62 state=2

[MCU2_1] 12.417033 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_1] 12.417060 s: VHWA: DOF Init ... !!!

[MCU2_1] 12.420607 s: VHWA: DOF Init ... Done !!!

[MCU2_1] 12.420640 s: VHWA: SDE Init ... !!!

[MCU2_1] 12.422082 s: VHWA: SDE Init ... Done !!!

[MCU2_1] 12.422113 s: VHWA: DMPAC: Init ... Done !!!

[MCU2_1] 12.422149 s: VX_ZONE_INIT:Enabled

[MCU2_1] 12.422173 s: VX_ZONE_ERROR:Enabled

[MCU2_1] 12.422195 s: VX_ZONE_WARNING:Enabled

[MCU2_1] 12.423331 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target MCU2-1

[MCU2_1] 12.423551 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target DMPAC_SDE

[MCU2_1] 12.423745 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target DMPAC_DOF

[MCU2_1] 12.423789 s: VX_ZONE_INIT:[tivxInitLocal:130] Initialization Done !!!

[MCU2_1] 12.423819 s: APP: OpenVX Target kernel init ... !!!

[MCU2_1] 12.424082 s: APP: OpenVX Target kernel init ... Done !!!

[MCU2_1] 12.424112 s: UDMA Copy: Init ... !!!

[MCU2_1] 12.425251 s: UDMA Copy: Init ... Done !!!

[MCU2_1] 12.425291 s: APP: Init ... Done !!!

[MCU2_1] 12.425316 s: APP: Run ... !!!

[MCU2_1] 12.425336 s: IPC: Starting echo test ...

[MCU2_1] 12.427882 s: APP: Run ... Done !!!

[MCU2_1] 12.428566 s: IPC: Echo status: mpu1_0[x] mcu1_0[.] mcu2_0[x] mcu2_1[s] C7X_1[P] C7X_2[.]

[MCU2_1] 12.428645 s: IPC: Echo status: mpu1_0[x] mcu1_0[.] mcu2_0[x] mcu2_1[s] C7X_1[P] C7X_2[P]

[MCU2_1] 12.428715 s: IPC: Echo status: mpu1_0[x] mcu1_0[P] mcu2_0[x] mcu2_1[s] C7X_1[P] C7X_2[P]

[C7x_1 ] 4.635349 s: CIO: Init ... Done !!!

[C7x_1 ] 4.635366 s: ### CPU Frequency = 1000000000 Hz

[C7x_1 ] 4.635378 s: CPU is running FreeRTOS

[C7x_1 ] 4.635386 s: APP: Init ... !!!

[C7x_1 ] 4.635394 s: SCICLIENT: Init ... !!!

[C7x_1 ] 4.635501 s: SCICLIENT: DMSC FW version [8.6.3--v08.06.03 (Chill Capybar]

[C7x_1 ] 4.635516 s: SCICLIENT: DMSC FW revision 0x8

[C7x_1 ] 4.635526 s: SCICLIENT: DMSC FW ABI revision 3.1

[C7x_1 ] 4.635538 s: SCICLIENT: Init ... Done !!!

[C7x_1 ] 4.635547 s: UDMA: Init ... !!!

[C7x_1 ] 4.636395 s: UDMA: Init ... Done !!!

[C7x_1 ] 4.636408 s: MEM: Init ... !!!

[C7x_1 ] 4.636420 s: MEM: Created heap (DDR_LOCAL_MEM, id=0, flags=0x00000004) @ 117000000 of size 268435456 bytes !!!

[C7x_1 ] 4.636442 s: MEM: Created heap (L3_MEM, id=1, flags=0x00000001) @ 70020000 of size 3964928 bytes !!!

[C7x_1 ] 4.636461 s: MEM: Created heap (L2_MEM, id=2, flags=0x00000001) @ 64800000 of size 458752 bytes !!!

[C7x_1 ] 4.636479 s: MEM: Created heap (L1_MEM, id=3, flags=0x00000001) @ 64e00000 of size 16384 bytes !!!

[C7x_1 ] 4.636496 s: MEM: Created heap (DDR_SCRATCH_MEM, id=4, flags=0x00000001) @ 100000000 of size 385875968 bytes !!!

[C7x_1 ] 4.636515 s: MEM: Init ... Done !!!

[C7x_1 ] 4.636523 s: IPC: Init ... !!!

[C7x_1 ] 4.636537 s: IPC: 6 CPUs participating in IPC !!!

[C7x_1 ] 4.636552 s: IPC: Waiting for HLOS to be ready ... !!!

[C7x_1 ] 11.664710 s: IPC: HLOS is ready !!!

[C7x_1 ] 11.667085 s: IPC: Init ... Done !!!

[C7x_1 ] 11.667100 s: APP: Syncing with 5 CPUs ... !!!

[C7x_1 ] 12.414917 s: APP: Syncing with 5 CPUs ... Done !!!

[C7x_1 ] 12.414937 s: REMOTE_SERVICE: Init ... !!!

[C7x_1 ] 12.415129 s: REMOTE_SERVICE: Init ... Done !!!

[C7x_1 ] 12.415159 s: VX_ZONE_INIT:Enabled

[C7x_1 ] 12.415207 s: VX_ZONE_ERROR:Enabled

[C7x_1 ] 12.415220 s: VX_ZONE_WARNING:Enabled

[C7x_1 ] 12.415534 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1

[C7x_1 ] 12.415653 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_2

[C7x_1 ] 12.415729 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_3

[C7x_1 ] 12.415803 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_4

[C7x_1 ] 12.415894 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_5

[C7x_1 ] 12.415972 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_6

[C7x_1 ] 12.416049 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_7

[C7x_1 ] 12.416130 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_8

[C7x_1 ] 12.416156 s: VX_ZONE_INIT:[tivxInitLocal:130] Initialization Done !!!

[C7x_1 ] 12.416171 s: APP: OpenVX Target kernel init ... !!!

[C7x_1 ] 12.416317 s: APP: OpenVX Target kernel init ... Done !!!

[C7x_1 ] 12.416332 s: APP: Init ... Done !!!

[C7x_1 ] 12.416343 s: APP: Run ... !!!

[C7x_1 ] 12.416352 s: IPC: Starting echo test ...

[C7x_1 ] 12.416528 s: APP: Run ... Done !!!

[C7x_1 ] 12.417753 s: IPC: Echo status: mpu1_0[x] mcu1_0[x] mcu2_0[x] mcu2_1[x] C7X_1[s] C7X_2[P]

[C7x_1 ] 12.423291 s: IPC: Echo status: mpu1_0[x] mcu1_0[P] mcu2_0[x] mcu2_1[x] C7X_1[s] C7X_2[P]

[C7x_1 ] 12.428421 s: IPC: Echo status: mpu1_0[x] mcu1_0[P] mcu2_0[x] mcu2_1[P] C7X_1[s] C7X_2[P]

[C7x_2 ] 5.062216 s: CIO: Init ... Done !!!

[C7x_2 ] 5.062233 s: ### CPU Frequency = 1000000000 Hz

[C7x_2 ] 5.062246 s: CPU is running FreeRTOS

[C7x_2 ] 5.062255 s: APP: Init ... !!!

[C7x_2 ] 5.062265 s: SCICLIENT: Init ... !!!

[C7x_2 ] 5.062372 s: SCICLIENT: DMSC FW version [8.6.3--v08.06.03 (Chill Capybar]

[C7x_2 ] 5.062388 s: SCICLIENT: DMSC FW revision 0x8

[C7x_2 ] 5.062398 s: SCICLIENT: DMSC FW ABI revision 3.1

[C7x_2 ] 5.062410 s: SCICLIENT: Init ... Done !!!

[C7x_2 ] 5.062419 s: UDMA: Init ... !!!

[C7x_2 ] 5.063268 s: UDMA: Init ... Done !!!

[C7x_2 ] 5.063283 s: MEM: Init ... !!!

[C7x_2 ] 5.063295 s: MEM: Created heap (DDR_LOCAL_MEM, id=0, flags=0x00000004) @ 127000000 of size 16777216 bytes !!!

[C7x_2 ] 5.063318 s: MEM: Created heap (L2_MEM, id=2, flags=0x00000001) @ 65800000 of size 458752 bytes !!!

[C7x_2 ] 5.063335 s: MEM: Created heap (L1_MEM, id=3, flags=0x00000001) @ 65e00000 of size 16384 bytes !!!

[C7x_2 ] 5.063353 s: MEM: Created heap (DDR_SCRATCH_MEM, id=4, flags=0x00000001) @ 128000000 of size 67108864 bytes !!!

[C7x_2 ] 5.063372 s: MEM: Init ... Done !!!

[C7x_2 ] 5.063381 s: IPC: Init ... !!!

[C7x_2 ] 5.063396 s: IPC: 6 CPUs participating in IPC !!!

[C7x_2 ] 5.063411 s: IPC: Waiting for HLOS to be ready ... !!!

[C7x_2 ] 11.805805 s: IPC: HLOS is ready !!!

[C7x_2 ] 11.808222 s: IPC: Init ... Done !!!

[C7x_2 ] 11.808237 s: APP: Syncing with 5 CPUs ... !!!

[C7x_2 ] 12.414917 s: APP: Syncing with 5 CPUs ... Done !!!

[C7x_2 ] 12.414939 s: REMOTE_SERVICE: Init ... !!!

[C7x_2 ] 12.415155 s: REMOTE_SERVICE: Init ... Done !!!

[C7x_2 ] 12.415218 s: VX_ZONE_INIT:Enabled

[C7x_2 ] 12.415233 s: VX_ZONE_ERROR:Enabled

[C7x_2 ] 12.415245 s: VX_ZONE_WARNING:Enabled

[C7x_2 ] 12.415880 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP-1

[C7x_2 ] 12.415904 s: VX_ZONE_INIT:[tivxInitLocal:130] Initialization Done !!!

[C7x_2 ] 12.415917 s: APP: OpenVX Target kernel init ... !!!

[C7x_2 ] 12.416219 s: APP: OpenVX Target kernel init ... Done !!!

[C7x_2 ] 12.416238 s: UDMA Copy: Init ... !!!

[C7x_2 ] 12.417266 s: UDMA Copy: Init ... Done !!!

[C7x_2 ] 12.417282 s: APP: Init ... Done !!!

[C7x_2 ] 12.417292 s: APP: Run ... !!!

[C7x_2 ] 12.417301 s: IPC: Starting echo test ...

[C7x_2 ] 12.417462 s: APP: Run ... Done !!!

[C7x_2 ] 12.417761 s: IPC: Echo status: mpu1_0[x] mcu1_0[x] mcu2_0[x] mcu2_1[x] C7X_1[P] C7X_2[s]

[C7x_2 ] 12.423331 s: IPC: Echo status: mpu1_0[x] mcu1_0[P] mcu2_0[x] mcu2_1[x] C7X_1[P] C7X_2[s]

[C7x_2 ] 12.428435 s: IPC: Echo status: mpu1_0[x] mcu1_0[P] mcu2_0[x] mcu2_1[P] C7X_1[P] C7X_2[s]

Dear Brijesh,

after add prm.display_type = 0x100 , CSL_REG32_RD will hang. Please help me check.

Dss_init-->Dss_dctrlDrvInit-->Dss_evtMgrRegister-->Dss_evtMgrFillInfo-->Dss_enableL1Event->CSL_REG32_RD(&commRegs->VP_IRQSTATUS_0)

int32_t Dss_enableL1Event(Dss_EvtMgrInfo *evtMgrInfo,

uint32_t dssCommonRegionId,

uint32_t eventGroup,

uint32_t event,

uint32_t eventCnt)

{

int32_t retVal = FVID2_SOK;

uint32_t regVal;

CSL_dss_commRegs *commRegs;

const Dss_SocInfo *socInfo;

GT_assert(DssTrace, (NULL != evtMgrInfo));

/* Get common register space */

socInfo = Dss_getSocInfo();

commRegs = socInfo->commRegs[dssCommonRegionId];

GT_assert(DssTrace, (NULL != commRegs));

GT_0trace(DssTrace, GT_ERR, "qindh 1 Dss_enableL1Event........\r\n");

if(DSS_EVENT_GROUP_VP1 == eventGroup)

{

/* Clear the status of interrupt */

GT_0trace(DssTrace, GT_ERR, "qindh 1.0 Dss_enableL1Event........\r\n");

regVal = CSL_REG32_RD(&commRegs->VP_IRQSTATUS_0); //stuck here.....Hi Qin,

Can you please add prints to print value of commRegs and &commRegs->VP_IRQSTATUS_0? Just want to see if they contain correct DSS register offsets.

Most likely this is the first register access of the DSS in the driver, so if it still stuck here, DSS is not powered on.

From the Linux prompt, can you please use k3conf or devmem2 utility and try reading some DSS register?

Regards,

Brijesh

&commRegs->VP_IRQSTATUS_0 value is : 4a00068

root@j721s2-evm:/opt/vision_apps# devmem2 4a00068

/dev/mem opened.

Memory mapped at address 0xffffbaeb4000.

Read at address 0x00000004 (0xffffbaeb4004): 0x00000000

Dear Brijesh,

Is my modification correct?

--- a/vision_apps/platform/j721s2/rtos/common/app_cfg_mcu2_0.h

+++ b/vision_apps/platform/j721s2/rtos/common/app_cfg_mcu2_0.h

@@ -96,7 +96,7 @@

/* define below to enable DSI display, make sure to undef ENABLE_DSS_HDMI

& ENABLE_DSS_EDP as well */

#undef ENABLE_DSS_DSI

- #undef ENABLE_DSS_SINGLE

+ //#undef ENABLE_DSS_SINGLE

#undef ENABLE_DSS_EDP

#define ENABLE_I2C

#define ENABLE_BOARD

#ifdef BUILD_MCU_BOARD_DEPENDENCIES

#define ENABLE_CSI2RX

#define ENABLE_CSI2TX

/* IMPORANT NOTE:

* - Only one of ENABLE_DSS_SINGLE or ENABLE_DSS_DUAL should be defined

* - When ENABLE_DSS_SINGLE is defined, only one of ENABLE_DSS_HDMI or ENABLE_DSS_EDP should be defined

* - When ENABLE_DSS_DUAL is defined, ENABLE_DSS_HDMI and ENABLE_DSS_EDP are not used, both EDP and HDMI are enabled unconditionally

*/

#define ENABLE_DSS_SINGLE

#undef ENABLE_DSS_DUAL

/* define below to enable eDP display,

make sure to undef ENABLE_DSS_HDMI & ENABLE_DSS_DSI as well */

#define ENABLE_DSS_EDP

/* define below to enable HDMI display,

make sure to undef ENABLE_DSS_EDP & ENABLE_DSS_DSI as well */

#undef ENABLE_DSS_HDMI

/* define below to enable DSI display, make sure to undef ENABLE_DSS_HDMI

& ENABLE_DSS_EDP as well */

#undef ENABLE_DSS_DSI

//#undef ENABLE_DSS_SINGLE

#undef ENABLE_DSS_EDP

#define ENABLE_I2C

#define ENABLE_BOARD

#define ENABLE_GPIO

#else

#undef ENABLE_CSI2RX

#undef ENABLE_CSI2TX

#undef ENABLE_DSS_SINGLE

#undef ENABLE_DSS_DUAL

#undef ENABLE_DSS_EDP

#undef ENABLE_DSS_HDMI

#undef ENABLE_DSS_DSI

#undef ENABLE_I2C

#undef ENABLE_BOARD

#undef ENABLE_GPIO

#endifDear Brijesh,

M2M now is ok, and can save 1920x1080 UYVY image, But CSITx can not output image.

Hi Qin,

ok, what was the issue for DSS M2M?

What do you mean by CSITX is not outputting the image? Are you seeing frames being submitted to the CSITX? can you please get the performance stats and lets see if graph is running fine?

Regards,

Brijesh

what was the issue for DSS M2M?

--> use DSS_SINGLE and DSS_EDP at the same time.

//#undef ENABLE_DSS_SINGLE

//#undef ENABLE_DSS_EDP

Summary of CPU load,

====================

CPU: mpu1_0: TOTAL LOAD = 0.52 % ( HWI = 0. 7 %, SWI = 0. 0 % )

CPU: mcu1_0: TOTAL LOAD = 5. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

CPU: mcu2_0: TOTAL LOAD = 3. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

CPU: mcu2_1: TOTAL LOAD = 3. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

CPU: c7x_1: TOTAL LOAD = 0. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

CPU: c7x_2: TOTAL LOAD = 0. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

HWA performance statistics,

===========================

HWA: VISS: LOAD = 34.99 % ( 239 MP/s )

HWA: MSC0: LOAD = 50.30 % ( 355 MP/s )

DDR performance statistics,

===========================

DDR: READ BW: AVG = 1061 MB/s, PEAK = 6935 MB/s

DDR: WRITE BW: AVG = 1052 MB/s, PEAK = 1911 MB/s

DDR: TOTAL BW: AVG = 2113 MB/s, PEAK = 8846 MB/s

Detailed CPU performance/memory statistics,

===========================================

DDR_SHARED_MEM: Alloc's: 28 alloc's of 161865113 bytes

DDR_SHARED_MEM: Free's : 0 free's of 0 bytes

DDR_SHARED_MEM: Open's : 28 allocs of 161865113 bytes

DDR_SHARED_MEM: Total size: 536870912 bytes

CPU: mcu1_0: TASK: IPC_RX: 0. 0 %

CPU: mcu1_0: TASK: REMOTE_SRV: 0. 0 %

CPU: mcu1_0: TASK: LOAD_TEST: 0. 0 %

CPU: mcu1_0: TASK: IPC_TEST_RX: 0. 0 %

CPU: mcu1_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu1_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu1_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu1_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu1_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu1_0: HEAP: DDR_LOCAL_MEM: size = 8388608 B, free = 8388352 B ( 99 % unused)

CPU: mcu2_0: TASK: IPC_RX: 0. 0 %

CPU: mcu2_0: TASK: REMOTE_SRV: 0.16 %

CPU: mcu2_0: TASK: LOAD_TEST: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CPU_0: 0.34 %

CPU: mcu2_0: TASK: TIVX_V1NF: 0. 0 %

CPU: mcu2_0: TASK: TIVX_V1LDC1: 0. 0 %

CPU: mcu2_0: TASK: TIVX_V1SC1: 0. 0 %

CPU: mcu2_0: TASK: TIVX_V1MSC2: 0. 0 %

CPU: mcu2_0: TASK: TIVXVVISS1: 0. 1 %

CPU: mcu2_0: TASK: TIVX_CAPT1: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT2: 0. 0 %

CPU: mcu2_0: TASK: TIVX_DISP1: 0. 0 %

CPU: mcu2_0: TASK: TIVX_DISP2: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CSITX: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CSITX2: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT3: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT4: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT5: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT6: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT7: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT8: 0. 0 %

CPU: mcu2_0: TASK: TIVX_DPM2M1: 0. 0 %

CPU: mcu2_0: TASK: TIVX_DPM2M2: 0. 0 %

CPU: mcu2_0: TASK: TIVX_DPM2M3: 0. 0 %

CPU: mcu2_0: HEAP: DDR_LOCAL_MEM: size = 16777216 B, free = 16046592 B ( 95 % unused)

CPU: mcu2_0: HEAP: L3_MEM: size = 524288 B, free = 524032 B ( 99 % unused)

CPU: mcu2_1: TASK: IPC_RX: 0. 0 %

CPU: mcu2_1: TASK: REMOTE_SRV: 0. 0 %

CPU: mcu2_1: TASK: LOAD_TEST: 0. 0 %

CPU: mcu2_1: TASK: TIVX_CPU_1: 0. 0 %

CPU: mcu2_1: TASK: TIVX_SDE: 0. 0 %

CPU: mcu2_1: TASK: TIVX_DOF: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_RX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: HEAP: DDR_LOCAL_MEM: size = 16777216 B, free = 16773120 B ( 99 % unused)

CPU: mcu2_1: HEAP: L3_MEM: size = 524288 B, free = 524288 B (100 % unused)

CPU: c7x_1: TASK: IPC_RX: 0. 0 %

CPU: c7x_1: TASK: REMOTE_SRV: 0. 0 %

CPU: c7x_1: TASK: LOAD_TEST: 0. 0 %

CPU: c7x_1: TASK: TIVX_C71_P1: 0. 0 %

CPU: c7x_1: TASK: TIVX_C71_P2: 0. 0 %

CPU: c7x_1: TASK: TIVX_C71_P3: 0. 0 %

CPU: c7x_1: TASK: TIVX_C71_P4: 0. 0 %

CPU: c7x_1: TASK: TIVX_C71_P5: 0. 0 %

CPU: c7x_1: TASK: TIVX_C71_P6: 0. 0 %

CPU: c7x_1: TASK: TIVX_C71_P7: 0. 0 %

CPU: c7x_1: TASK: TIVX_C71_P8: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_RX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

[MCU1_0] 405.271147 s: RTOS IPC: user_callback, src_cpu:0, payload:0, src_port:1024.

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

[MCU1_0] 405.271234 s: RTOS IPC: user_callback, src_cpu:0, payload:0, src_port:1024.

[MCU1_0] 405.271297 s: RTOS IPC: user_callback, src_cpu:0, payload:0, src_port:1024.

CPU: c7x_1: HEAP: DDR_LOCAL_MEM: size = 268435456 B, free = 268435200 B ( 99 % unused)

CPU: c7x_1: HEAP: L3_MEM: size = 3964928 B, free = 3964928 B (100 % unused)

CPU: c7x_1: HEAP: L2_MEM: size = 458752 B, free = 458752 B (100 % unused)

CPU: c7x_1: HEAP: L1_MEM: size = 16384 B, free = 16384 B (100 % unused)

CPU: c7x_1: HEAP: DDR_SCRATCH_MEM: size = 385875968 B, free = 385875968 B (100 % unused)

CPU: c7x_2: TASK: IPC_RX: 0. 0 %

CPU: c7x_2: TASK: REMOTE_SRV: 0. 0 %

CPU: c7x_2: TASK: LOAD_TEST: 0. 0 %

CPU: c7x_2: TASK: TIVX_CPU: 0. 0 %

CPU: c7x_2: TASK: IPC_TEST_RX: 0. 0 %

CPU: c7x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_2: HEAP: DDR_LOCAL_MEM: size = 16777216 B, free = 16772608 B ( 99 % unused)

CPU: c7x_2: HEAP: L2_MEM: size = 458752 B, free = 458752 B (100 % unused)

CPU: c7x_2: HEAP: L1_MEM: size = 16384 B, free = 16384 B (100 % unused)

CPU: c7x_2: HEAP: DDR_SCRATCH_MEM: size = 67108864 B, free = 67108864 B (100 % unused)

GRAPH: graph_85 (#nodes = 6, #executions = 68)

NODE: CAPTURE2: node_96: avg = 33654 usecs, min/max = 33218 / 58809 usecs, #executions = 68

NODE: VPAC_VISS1: VISS_Processing: avg = 12648 usecs, min/max = 12418 / 12863 usecs, #executions = 68

NODE: MCU2-0: 2A_AlgNode: avg = 24504 usecs, min/max = 24472 / 24908 usecs, #executions = 68

NODE: VPAC_MSC1: node_107: avg = 17658 usecs, min/max = 17622 / 17788 usecs, #executions = 68

NODE: DSS_M2M1: FmtConvNode: avg = 3774 usecs, min/max = 3765 / 3871 usecs, #executions = 68

NODE: CSITX2: node_113: avg = 21896 usecs, min/max = 21886 / 22001 usecs, #executions = 68

PERF: TOTAL: avg = 33316 usecs, min/max = 32829 / 33572 usecs, #executions = 68

PERF: TOTAL: 30. 1 FPS

[MCU2_0] 485.061498 s: ==========================================================

[MCU2_0] 485.061542 s: Capture Status: Instance|0

[MCU2_0] 485.061567 s: ==========================================================

[MCU2_0] 485.061602 s: overflowCount: 0

[MCU2_0] 485.061631 s: spuriousUdmaIntrCount: 0

[MCU2_0] 485.061660 s: frontFIFOOvflCount: 0

[MCU2_0] 485.061687 s: crcCount: 0

[MCU2_0] 485.061712 s: eccCount: 0

[MCU2_0] 485.061739 s: correctedEccCount: 0

[MCU2_0] 485.061767 s: dataIdErrorCount: 0

[MCU2_0] 485.061795 s: invalidAccessCount: 0

[MCU2_0] 485.061823 s: invalidSpCount: 0

[MCU2_0] 485.061856 s: strmFIFOOvflCount[0]: 0

[MCU2_0] 485.061889 s: strmFIFOOvflCount[1]: 0

[MCU2_0] 485.061914 s: Channel Num | Frame Queue Count | Frame De-queue Count | Frame Drop Count | Error Frame Count |

[MCU2_0] 485.062356 s: ==========================================================

[MCU2_0] 485.062407 s: Capture Status: Instance|1

[MCU2_0] 485.062431 s: ==========================================================

[MCU2_0] 485.062467 s: overflowCount: 0

[MCU2_0] 485.062496 s: spuriousUdmaIntrCount: 0

[MCU2_0] 485.062525 s: frontFIFOOvflCount: 0

[MCU2_0] 485.062552 s: crcCount: 0

[MCU2_0] 485.062577 s: eccCount: 0

[MCU2_0] 485.062603 s: correctedEccCount: 0

[MCU2_0] 485.062631 s: dataIdErrorCount: 0

[MCU2_0] 485.062659 s: invalidAccessCount: 0

[MCU2_0] 485.062687 s: invalidSpCount: 0

[MCU2_0] 485.062719 s: strmFIFOOvflCount[0]: 0

[MCU2_0] 485.062752 s: strmFIFOOvflCount[1]: 0

[MCU2_0] 485.062776 s: Channel Num | Frame Queue Count | Frame De-queue Count | Frame Drop Count | Error Frame Count |

[MCU2_0] 485.062840 s: 0 | 2452 | 2452 | 1 | 0 |

[MCU2_0] 485.063621 s: CsitxDrv_control = 6

[MCU2_0] 485.063789 s: CsitxDrv_control = 268451840

[MCU2_0] 485.063826 s: ==========================================================

[MCU2_0] 485.063865 s: Csitx Status: Instance|1

[MCU2_0] 485.063888 s: ==========================================================

[MCU2_0] 485.063925 s: FIFO Overflow Count: 0

[MCU2_0] 485.063949 s: Channel Num | Frame Queue Count | Frame De-queue Count | Frame Repeat Count |

[MCU2_0] 485.064001 s: 0| 2450| 2450| 0|

[MCU2_0] 485.064502 s: ==========================================================

[MCU2_0] 485.064560 s: Display M2M Status: Instance|0

[MCU2_0] 485.064586 s: ==========================================================

[MCU2_0] 485.064622 s: Queue Count: 2450

[MCU2_0] 485.064650 s: De-queue Count: 2450

[MCU2_0] 485.064680 s: Write-back Frames Count: 2450

[MCU2_0] 485.064710 s: Underflow Count: 0

Dear Brijesh,

Could you hlep me check my code ? How to check frames being submitted to the CSITX?

Hi Qin,

The code looks to be fine to me. The output object array of DSS M2M is used as input to CSITX node. This is correct. In the performance stats that you shared earlier, I see that CSITX node is running and submitting the frames at every 21.8ms.. So it seems to be running fine.

NODE: CSITX2: node_113: avg = 21896 usecs, min/max = 21886 / 22001 usecs, #executions = 68

Apart from this, I see that you are using CSITX Instance-1. for this instance, can you please set below configuration is taken care? Please check if this register is set to 0x1.

/* Select CSITX1 as the source for DPHYTX1 */

CSL_REG32_WR(CSL_CTRL_MMR0_CFG0_BASE +

CSL_MAIN_CTRL_MMR_CFG0_DPHY_TX1_CTRL,

0x1);

Regards,

Brijesh

Dear Brijesh,

I have previously verified that YUV Camera can output images to CSITx,so I think CSITx configure is ok.

Dear Brijesh,

Thank you very much for your support, Now 8M raw camera can output 2M UYVY image to CSITx, and CSITx is working fine.

ok, could you help me understand what's changed for CSITX to get working? Anything in usecase or driver do you have to change?

Dear Brijesh,

Removed CSITx Enqueue and Deque, Than CSITx working fine.

if(status == VX_SUCCESS)

{

status = vxGraphParameterDequeueDoneRef(obj->graph, graph_parameter_num, (vx_reference*)&out_capture_frames, 1, &num_refs_capture);

}

#if 0

if(status == VX_SUCCESS)

{

status = vxGraphParameterDequeueDoneRef(obj->graph, 1, (vx_reference*)&transmitted_frames, 1, &num_refs);

}

#endif

graph_parameter_num++;

if((status == VX_SUCCESS) && (obj->test_mode == 1))

{

status = vxGraphParameterDequeueDoneRef(obj->graph, 1, (vx_reference*)&test_image, 1, &num_refs_capture);

}

graph_parameter_num = 0;

if((status == VX_SUCCESS) && (obj->test_mode == 1))

{

status = vxGraphParameterEnqueueReadyRef(obj->graph, 1, (vx_reference*)&test_image, 1);

}

#if 0

if(status == VX_SUCCESS)

{

status = vxGraphParameterEnqueueReadyRef(obj->graph, graph_parameter_num, (vx_reference*)&out_capture_frames, 1);

}

#endif

if(status == VX_SUCCESS)

{

status = vxGraphParameterEnqueueReadyRef(obj->graph, 1, (vx_reference*)&transmitted_frames, 1);

}

graph_parameter_num++;