Part Number: AM64x/AM62x/AM62Ax

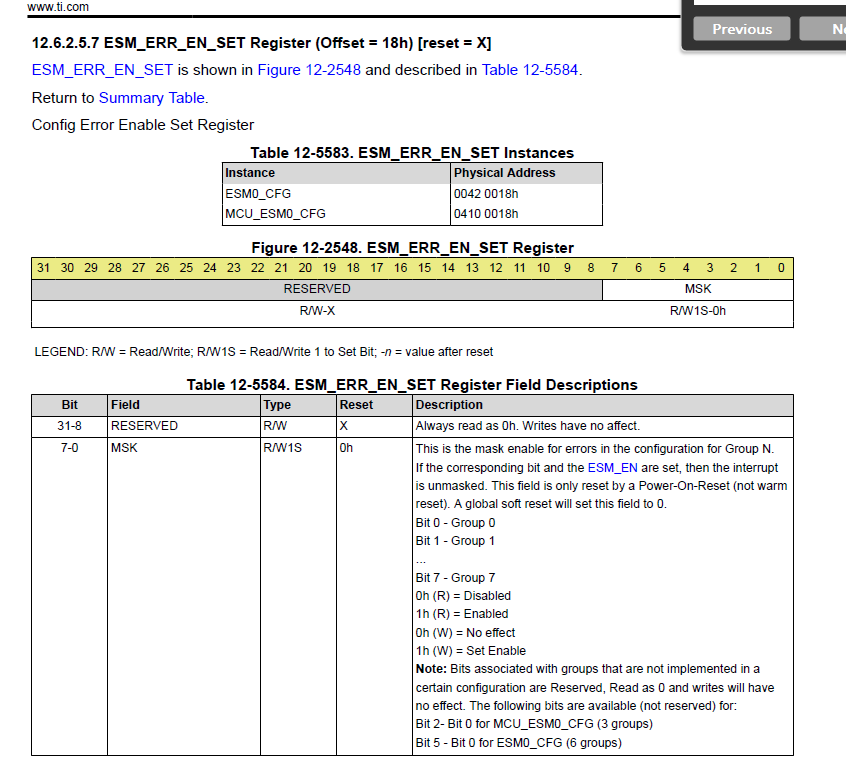

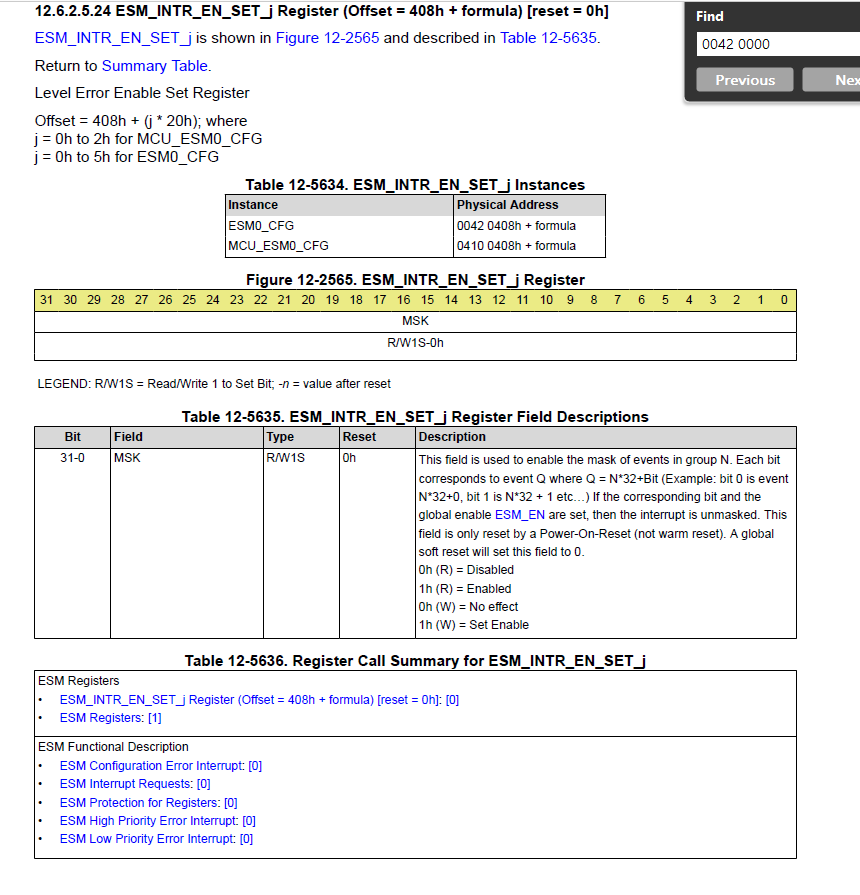

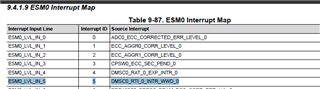

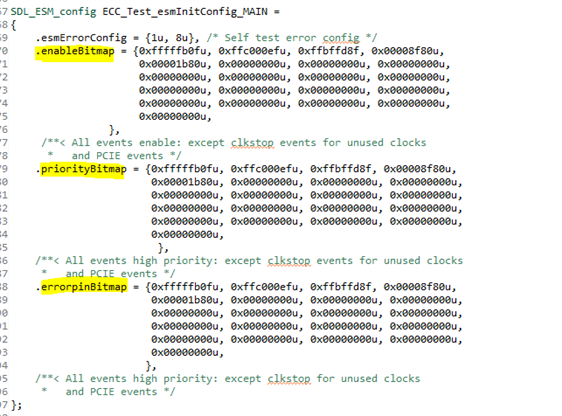

This FAQ mainly explains how to configure the ESM module in the SDL and enabling the error events which trigger the ESM interrupts.

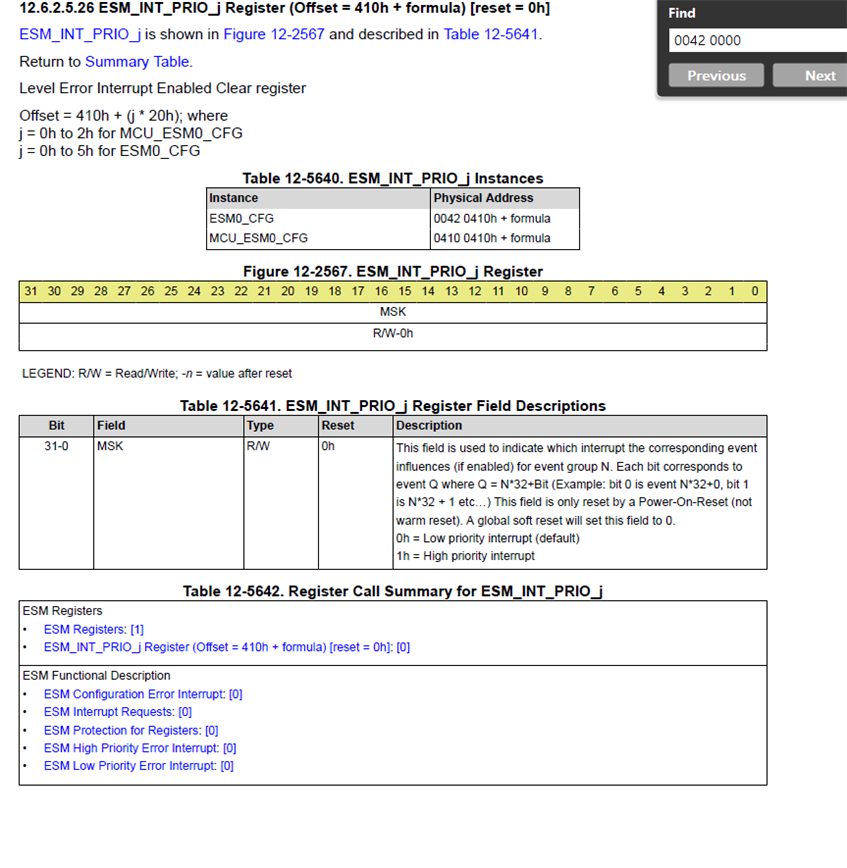

It also shows how to set a interrupt priority for an ESM event and enable an external error pin for the corresponding event.

The below explanation would be applicable for AM64x,AM62x and AM62Ax devices.