Tool/software:

Hi support team.

I'm working now on the product based on the AM62x processor.

When reading the datasheet I spotted some information that can affect my design.

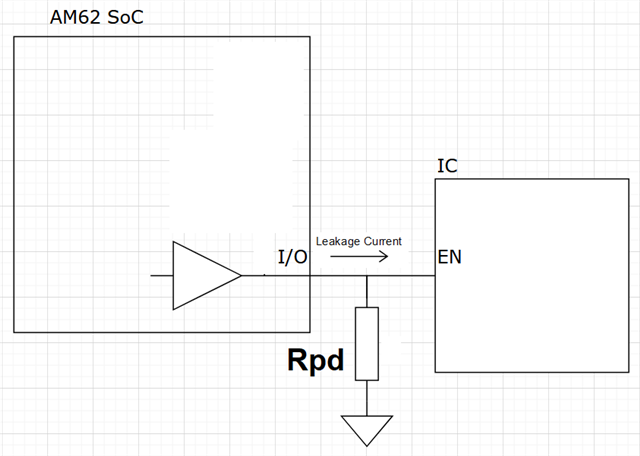

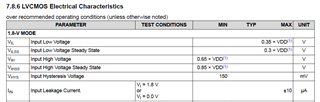

Does the leakage current for the I/O pins really can go up to 10uA? In which condition.

Please help me understand.

How big leakage current for the I/O pin I should expect when the CPU is in the Reset state?

As an example lets take a GPMC0_CLK (P25) pin used as an Output. How big leakage current I should expect for this pin in a Reset state?

Thank you.